- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- 製品フォーラム

- :

- デジタルシグナルコントローラ

- :

- How to understand I/O status for 56F827XX at reset

How to understand I/O status for 56F827XX at reset

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

How to understand I/O status for 56F827XX at reset

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi:

here are several questions about datasheet

1.From latest DS for 56F827XX, <MC56F827XXDS>, there are some descriptions for I/O during reset.

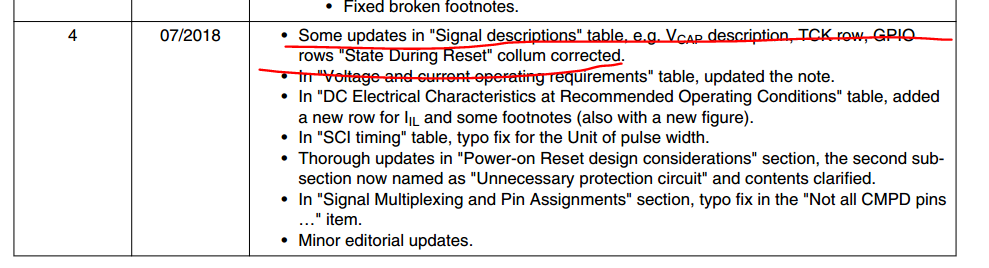

<Rev. 4, 07/2018> vs <Rev. 3.0, 09/2016 > , update IO status from "input, internal pull-up" to "input" for most GPIO, whether which means the input is tri-state(high impedance)?

2.this adjustment is for new silicon or all old products??

3.I noticed other old 56f825X datasheet also indicate internal-pull up, seems which is a classic design, why this pull-up cancelled?

4.How about warm reset(watchdog, SW reset), how these warm reset influence GPIO status during reset?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Dawei You,

I use the 82746 and it comes up in HiZ state at power on.

I was surprised at that since other DSC's I've used come up in Input state with Pullups (normal).

Not sure what happens after other reset sources but would imagine it is the same.

So if you require a certain state you need to add external pullups.

Pete