- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior开发工具

- :

- QSCI baudrate setting

QSCI baudrate setting

QSCI baudrate setting

Iam using Serial LDD component in Code worrier 11.1 and setting the baud rate of 115200 in the configuration but in actual generated code it is setting the baud rate as 57600 i.e., 1 index less in baud rate table, this is same for all baud rate, can I get a solution for this to set it as required.

Hi,

Hope it can help you

BR

XiangJun Rong

Hi,

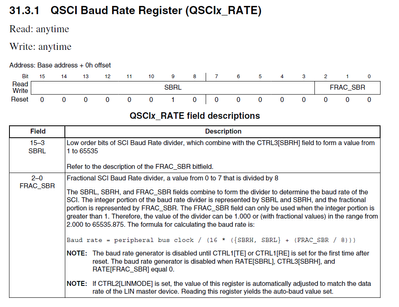

Okay, it appears that it is a bug of Processor Expert, in the debug, pls read the QSCIx_RATE register, and tell us the BUS_CLK clock frequency you are using, then compute the baud rate of SCI based on the BUS_CLK or 2XBUS_CLK.

If baud rate does not match with the expected, it is a bug of PE.

Hope it can help you

BR'

XiangJun Rong

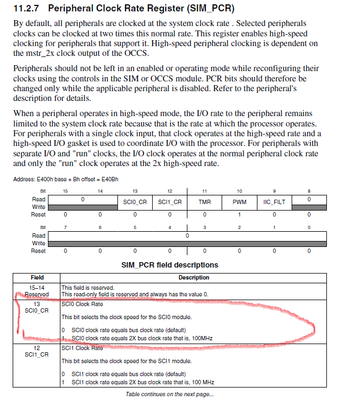

Iam using 30MHz of bus clock frequency and operating CPU in fast mode which intern sets core clock frequency and system clock frequency as 60MHz, and we debugged using both BUS_Clk and 2XBUS_Clck and got below values of QSCIx_RATE and QSCIx_CTRL3 registers respectively.

using BUS_CLk - 0104(RATE), 0000(CTRL3)

using 2XBUS_Clk - 0209(RATE), 0000(CTRL3)

and we also found that TimerInt_LDD component we are getting interrupt at double the time set in configuration that means if we configure it as 100us getting interrupt at 200us.

Hi,