- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- Software Forums

- :

- Processor Expert Software

- :

- Re: Processor Expert Version 10.4 and ADC measurements not working as expected.

Processor Expert Version 10.4 and ADC measurements not working as expected.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

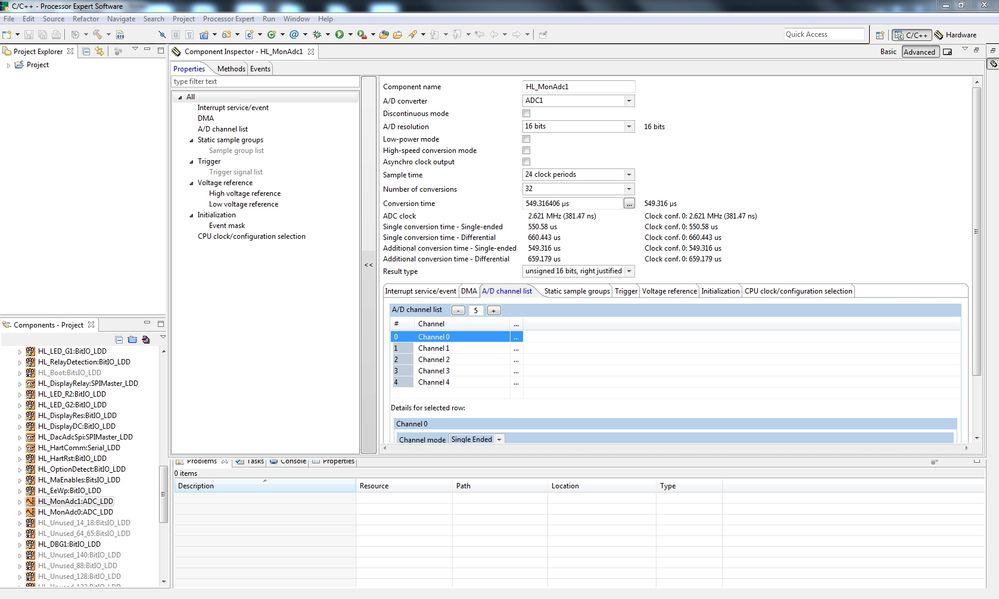

I am using the current PE10.4 with the MK10DN512VLL10 processor. I am setting 5 channels up as single ended inputs. The issue is that two channels read correctly and three channel read either full scale or zero.

The issue that I am seeing with PE10.4 is that the bit ADC_CFG2_MUXSEL_MASK in the ADCx_CFG2 register appears to only get set during initialization method. As you can see it is set several times during this initialization. It is not an arrayed byte so this doesn't make much since. In writing the code this way forces the hardware to either connect all of the ADC channels to "a" or "b" inputs. Since my hardware connect the first two channels to the "a" inputs and the last three inputs to the "b" channels the "b" channels cannot be read. See the code HL_MonAdc1_Init below: Is this limited by design or would it be better to set the correct ADC_CFG2_MUXSEL_MASK setting when the CreateSampleGroup method is called? This would allow any combination of ADC inputs to be measured for single ended devices.

Thanks,

Kevin.

LDD_TDeviceData* HL_MonAdc1_Init(LDD_TUserData *UserDataPtr)

{

/* Allocate LDD device structure */

HL_MonAdc1_TDeviceDataPtr DeviceDataPrv;

/* {Default RTOS Adapter} Driver memory allocation: Dynamic allocation is simulated by a pointer to the static object */

DeviceDataPrv = &DeviceDataPrv__DEFAULT_RTOS_ALLOC;

DeviceDataPrv->UserData = UserDataPtr; /* Store the RTOS device structure */

DeviceDataPrv->SampleCount = 0U; /* Initializing SampleCount for right access of some methods to SC1n registers before first conversion is done */

/* SIM_SCGC3: ADC1=1 */

SIM_SCGC3 |= SIM_SCGC3_ADC1_MASK;

/* PORTC_PCR10: ISF=0,MUX=0 */

PORTC_PCR10 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* ADC1_CFG2: MUXSEL=1 */

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

/* PORTC_PCR9: ISF=0,MUX=0 */

PORTC_PCR9 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* ADC1_CFG2: MUXSEL=1 */

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

/* PORTC_PCR8: ISF=0,MUX=0 */

PORTC_PCR8 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* ADC1_CFG2: MUXSEL=1 */

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

/* ADC1_CFG1: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,ADLPC=0,ADIV=3,ADLSMP=1,MODE=3,ADICLK=1 */

ADC1_CFG1 = ADC_CFG1_ADIV(0x03) |

ADC_CFG1_ADLSMP_MASK |

ADC_CFG1_MODE(0x03) |

ADC_CFG1_ADICLK(0x01);

/* ADC1_CFG2: MUXSEL=0,ADACKEN=0,ADHSC=0,ADLSTS=0 */

ADC1_CFG2 &= (uint32_t)~(uint32_t)(

ADC_CFG2_MUXSEL_MASK |

ADC_CFG2_ADACKEN_MASK |

ADC_CFG2_ADHSC_MASK |

ADC_CFG2_ADLSTS(0x03)

);

/* ADC1_SC2: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,ADACT=0,ADTRG=0,ACFE=0,ACFGT=0,ACREN=0,DMAEN=0,REFSEL=0 */

ADC1_SC2 = ADC_SC2_REFSEL(0x00);

/* ADC1_SC3: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,CAL=0,CALF=1,??=0,??=0,ADCO=0,AVGE=1,AVGS=3 */

ADC1_SC3 = (ADC_SC3_CALF_MASK | ADC_SC3_AVGE_MASK | ADC_SC3_AVGS(0x03));

/* Registration of the device structure */

PE_LDD_RegisterDeviceStructure(PE_LDD_COMPONENT_HL_MonAdc1_ID,DeviceDataPrv);

return ((LDD_TDeviceData *)DeviceDataPrv); /* Return pointer to the data data structure */

}

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please find attached a hot-fix package for Processor Expert Driver Suite 10.4, which fixes this problem.

Best regards

Petr Hradsky

Processor Expert Support Team

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Are you using CodeWarrior 10.4 or Processor Expert Driver Suite 10.4?

Currently, there is a limitation that Processor Expert does not allow to change MUXSEL in ADCx_CFG at runtime so the pins needs to be in the same multiplexer.

I have tried that in PEx Driver Suite 10.4 and there is an error reported and it's not allowed:

There was an issue with older versions of CodeWarrior that it has not been checked and it allowed this setup even though it didn't work.

Best regards

Petr Hradsky

Processor Expert Support Team

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using the Processor Expert Driver Suite 10.4. Mine is not showing an error here. These are my settings:

Channel 1:

PGA1_DM/ADC1_DM0/ADC0_DM3 - single ended

Channel 2:

VREF_OUT/CMP1_IN5/CMP0_IN5/ADC1_SE18 - single ended

Channel 3:

ADC1_SE6b/PTC10/I2C1_SCL/I2S0_RX_FS/FB_AD5 - single ended

Channel 4:

ADC1_SE5b/CMP0_IN3/PTC9/I2S0_RX_BCLK/FB_AD6/FTM2_FLT0 - single ended

Channel 5:

ADC1_SE4b/CMP0_IN2/PTC8/I2S0_MCLK/FB_AD7 - single ended

Also I have looked at this some more today by building PE10.2. I found the following:

I think the real issue is that a line of code was added from PE10.2 to PE10.4. It might not be an "a" "b" problem as much as you can never select the "b" channels anymore. See the ADC1_CFG2 &= statements below:

PE10.4 is now &= in ADC_CFG2_MUXSEL_MASK. This will always set the bit to 0 now.

Let me know if you have any additional questions.

Thanks,

Kevin.

PE V10.2

LDD_TDeviceData* HL_MonAdc1_Init(LDD_TUserData *UserDataPtr)

{

/* Allocate LDD device structure */

HL_MonAdc1_TDeviceDataPtr DeviceDataPrv;

/* {Default RTOS Adapter} Driver memory allocation: Dynamic allocation is simulated by a pointer to the static object */

DeviceDataPrv = &DeviceDataPrv__DEFAULT_RTOS_ALLOC;

DeviceDataPrv->UserData = UserDataPtr; /* Store the RTOS device structure */

DeviceDataPrv->SampleCount = 0U; /* Initializing SampleCount for right access of some methods to SC1n registers before first conversion is done */

/* SIM_SCGC3: ADC1=1 */

SIM_SCGC3 |= SIM_SCGC3_ADC1_MASK;

/* PORTC_PCR10: ISF=0,MUX=0 */

PORTC_PCR10 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* ADC1_CFG2: MUXSEL=1 */

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

/* PORTC_PCR9: ISF=0,MUX=0 */

PORTC_PCR9 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* ADC1_CFG2: MUXSEL=1 */

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

/* PORTC_PCR8: ISF=0,MUX=0 */

PORTC_PCR8 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* ADC1_CFG2: MUXSEL=1 */

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

/* ADC1_CFG1: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,ADLPC=0,ADIV=3,ADLSMP=1,MODE=3,ADICLK=1 */

ADC1_CFG1 = ADC_CFG1_ADIV(0x03) |

ADC_CFG1_ADLSMP_MASK |

ADC_CFG1_MODE(0x03) |

ADC_CFG1_ADICLK(0x01);

/* ADC1_CFG2: ADACKEN=0,ADHSC=0,ADLSTS=0 */

ADC1_CFG2 &= (uint32_t)~(uint32_t)(

ADC_CFG2_ADACKEN_MASK |

ADC_CFG2_ADHSC_MASK |

ADC_CFG2_ADLSTS(0x03)

);

/* ADC1_SC2: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,ADACT=0,ADTRG=0,ACFE=0,ACFGT=0,ACREN=0,DMAEN=0,REFSEL=0 */

ADC1_SC2 = ADC_SC2_REFSEL(0x00);

/* ADC1_SC3: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,CAL=0,CALF=1,??=0,??=0,ADCO=0,AVGE=1,AVGS=3 */

ADC1_SC3 = (ADC_SC3_CALF_MASK | ADC_SC3_AVGE_MASK | ADC_SC3_AVGS(0x03));

/* Registration of the device structure */

PE_LDD_RegisterDeviceStructure(PE_LDD_COMPONENT_HL_MonAdc1_ID,DeviceDataPrv);

return ((LDD_TDeviceData *)DeviceDataPrv); /* Return pointer to the data data structure */

}

PE10.4

LDD_TDeviceData* HL_MonAdc1_Init(LDD_TUserData *UserDataPtr)

{

/* Allocate LDD device structure */

HL_MonAdc1_TDeviceDataPtr DeviceDataPrv;

/* {Default RTOS Adapter} Driver memory allocation: Dynamic allocation is simulated by a pointer to the static object */

DeviceDataPrv = &DeviceDataPrv__DEFAULT_RTOS_ALLOC;

DeviceDataPrv->UserData = UserDataPtr; /* Store the RTOS device structure */

DeviceDataPrv->SampleCount = 0U; /* Initializing SampleCount for right access of some methods to SC1n registers before first conversion is done */

/* SIM_SCGC3: ADC1=1 */

SIM_SCGC3 |= SIM_SCGC3_ADC1_MASK;

/* PORTC_PCR10: ISF=0,MUX=0 */

PORTC_PCR10 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* ADC1_CFG2: MUXSEL=1 */

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

/* PORTC_PCR9: ISF=0,MUX=0 */

PORTC_PCR9 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* ADC1_CFG2: MUXSEL=1 */

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

/* PORTC_PCR8: ISF=0,MUX=0 */

PORTC_PCR8 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* ADC1_CFG2: MUXSEL=1 */

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

/* ADC1_CFG1: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,ADLPC=0,ADIV=3,ADLSMP=1,MODE=3,ADICLK=1 */

ADC1_CFG1 = ADC_CFG1_ADIV(0x03) |

ADC_CFG1_ADLSMP_MASK |

ADC_CFG1_MODE(0x03) |

ADC_CFG1_ADICLK(0x01);

/* ADC1_CFG2: MUXSEL=0,ADACKEN=0,ADHSC=0,ADLSTS=0 */

ADC1_CFG2 &= (uint32_t)~(uint32_t)(

ADC_CFG2_MUXSEL_MASK |

ADC_CFG2_ADACKEN_MASK |

ADC_CFG2_ADHSC_MASK |

ADC_CFG2_ADLSTS(0x03)

);

/* ADC1_SC2: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,ADACT=0,ADTRG=0,ACFE=0,ACFGT=0,ACREN=0,DMAEN=0,REFSEL=0 */

ADC1_SC2 = ADC_SC2_REFSEL(0x00);

/* ADC1_SC3: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,CAL=0,CALF=1,??=0,??=0,ADCO=0,AVGE=1,AVGS=3 */

ADC1_SC3 = (ADC_SC3_CALF_MASK | ADC_SC3_AVGE_MASK | ADC_SC3_AVGS(0x03));

/* Registration of the device structure */

PE_LDD_RegisterDeviceStructure(PE_LDD_COMPONENT_HL_MonAdc1_ID,DeviceDataPrv);

return ((LDD_TDeviceData *)DeviceDataPrv); /* Return pointer to the data data structure */

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you, now I see that it's a different issue. You have identified it correctly, there is a problem in the ADC_LDD initialization code in the latest Processor Expert Driver Suite 10.4.

It appears when you are using pins with 'b' (e.g. ADC0_SE4B). In such case the ADC_CFG2_MUXSEL field is incorrectly cleared in CFG2 register.

We are sorry for an inconvenience. The fix for the problem is being prepared and will be available in a short time.

As a temporary workaround, please place the following line after the AdcLdd1_Init call (or if you using "auto initialization" feature, after the /*** End of Processor Expert internal initialization. ):

In case you are using ADC0:

ADC0_CFG2 |= ADC_CFG2_MUXSEL_MASK;

In case you are using ADC1:

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

Best regards

Petr Hradsky

Processor Expert Support Team

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am having an issue with this same line of code. I am using an RTOS in my implementation and this line of code is being generated and executed before the ADC registers are activated. This results in a hard fault because the registers aren't available. Any help you can offer would be greatly appreciated.

ADC1_CFG2 |= ADC_CFG2_MUXSEL_MASK;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content