- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- DMA for Flexcomm SPI with 20-24-bit peripherals?

DMA for Flexcomm SPI with 20-24-bit peripherals?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DMA for Flexcomm SPI with 20-24-bit peripherals?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have what is a pretty common requirement for modern applications especially IOT.

Specifically, we need to, without code intervention - DMA only:

- read results from several SPI sensors

- interrupt (and possibly wake up sleeping) CPU after all the results are available in RAM

- the peripherals are 20-bit and 24-bit sensors (common for ADC and sensors like accelerometer, pressure, etc)

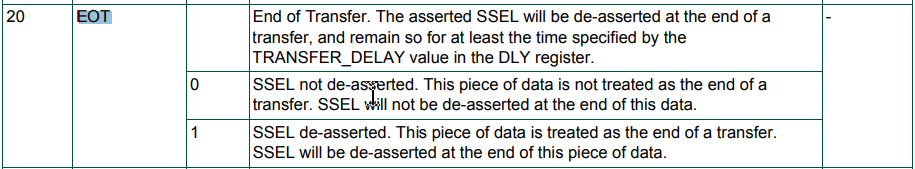

For each peripheral CS is asserted once, then 24 bits clocked in over SPI, and only after all data read CS de-asserted.

I was able to do this all with DMA+SPI on Kinetis K64F (DMA to sequence multiple CS toggling and multiple SPI xfers).

Successful products now shipping doing this on K64F ;-)

Now we're considering LPC55xxxx for next projects.

So, the question: Using DMA and flexcomm SPI, how does one accomplish this on LPC55xxx?

Flexcomm SPI documentation says:

'Data frames of 4 to 16 bits supported directly. Larger frames supported by software'

We need to read multiple 24-bit SPI devices before any interrupt. No multiple interrupts!

Only interrupt when all data read into RAM!

Thanks in advance for any pointers!

Best Regards, Dave

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello davenadler,

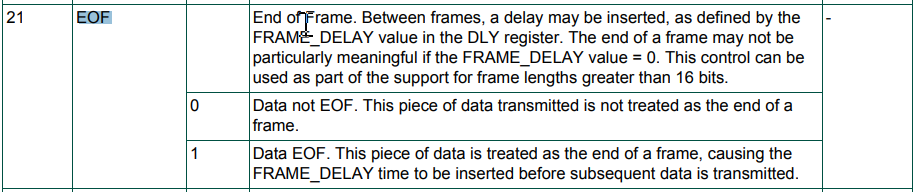

The reference manual mention the following regarding larger frames:

Larger sizes can be handled by splitting data up into groups of 16 bits or less. For example, 24 bits can be supported as two groups of 16 bits and 8 bits or two groups of 12 bits, among others. Frames of any size, including greater than 32 bits, can be supported in the same way.

Sending two groups of 12 bits with SSEL de-asserted between 24-bit increments, for instance, would require changing the value of the EOF bit on alternate 12-bit frames.

If you only want a single interruption between transfers you could try using the DMA interrupt instead of the SPI one.

Let me know if this helps you.

Best Regards,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Alexis, but you have not answered my question:

Using DMA and flexcomm SPI, how does one accomplish this on LPC55xxx?

How does one use DMA to sequence CS control and SPI operations to perform

for example a read from a 24-bit SPI device, with an interrupt only

when the data is read into RAM and ready to process?

Again, note CS must be asserted before clocking data, and de-asserted only after all 24-bits clocked in.

Thanks!

Best Regards, Dave

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello davenadler,

The EOF bit is used to manage the transmissions greater than 16 bits, so you will need to set this bit and set the FRAME_DELAY to 0, this way you could receive the full ADC frame as two transfers, or if you want as 3 8-bit transfers.

Also, if you need the SSEL is not asserted between transfers this bit could help you to do it.

In the SDK (link for download here), there's an example called spi_dma_b2b_transfer that you can use as reference.

I hope this helps you.

Best Regards,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Alexis for pointing out the deferred CS de-assert.

However, you still have not answered my question.

Again,

Using DMA and flexcomm SPI, how does one read (2) 24-bit SPI sensors without CPU intervention on LPC55xxx?

No interrupt until the data has been read into memory and is ready to process.

Thanks,

Best Regards, Dave