- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso General

- :

- Flexio for communication with ADS1222

Flexio for communication with ADS1222

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Flexio for communication with ADS1222

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

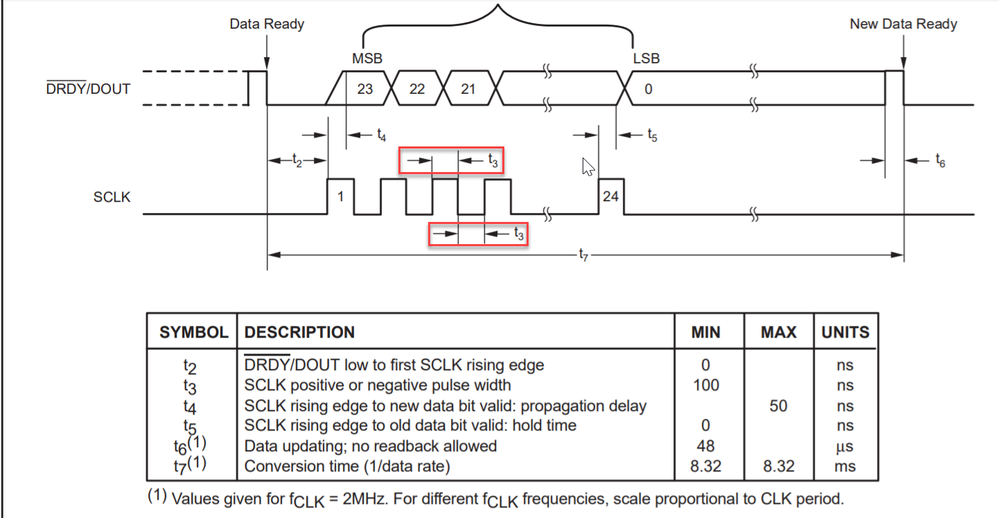

I am using a flexio to manage communication with ADS1222 24 bit Analog to digital converter.

One shifter for the serial data got on the DRDY/DOUT signal.

One timer generating shift clock and the SCLK clock signal

The trigger of the timer should be the falling edge of the DRDY/DOUT signal.

What's happening during timer decrementing if there are falling edges on the DRDY/DOUT signal ?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michele,

Could you tell us which MCU are you using?

Thanks in advance!

Best Regards,

Carlos Mendoza

Technical Support Engineer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

Thank you for your interest in my question. I’m using iMXRT1050.

Best regards

Michèle BLANC

Ingénieur logiciel

Tél : 04 72 78 35 72

mblanc@centralp.fr<mailto:mblanc@centralp.fr>

www.centralp.fr<http://www.centralp.fr/>;

De : Carlos_Mendoza

Envoyé : jeudi 10 janvier 2019 17:55

À : BLANC Michelle <mblanc@centralp.fr>

Objet : Re: - Re: Flexio for communication with ADS1222

NXP Community <https://community.freescale.com/resources/statics/1000/35400-NXP-Community-Email-banner-600x75.jpg>

Re: Flexio for communication with ADS1222

reply from Carlos_Mendoza<https://community.nxp.com/people/Carlos_Mendoza?et=watches.email.thread> in MCUXpresso Software and Tools - View the full discussion<https://community.nxp.com/message/1099919?commentID=1099919&et=watches.email.thread#comment-1099919>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

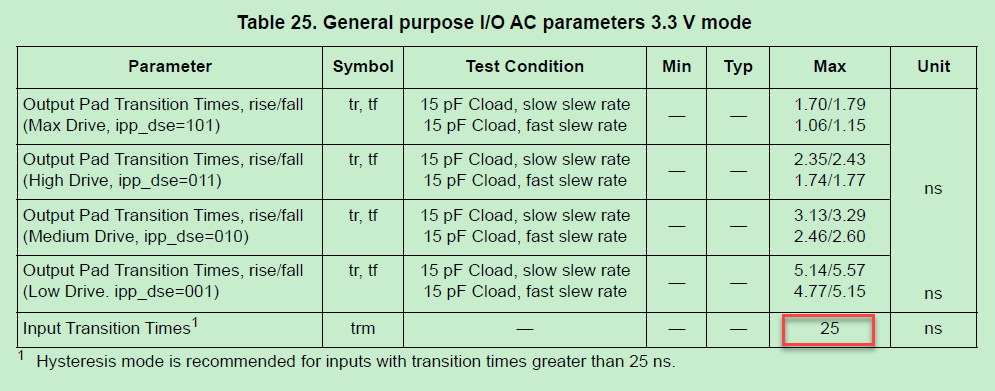

From i.MXRT1050 datasheet, the Max. input transition time is 25ns.

The ADS1222 using SCLK falling edge to sample the data, which required min. t3 value is 100ns.

There has enough time for FlexIO pin to capture the data value.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------