- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Clock PLL discipline using external 10MHz signal

Clock PLL discipline using external 10MHz signal

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using a MK22FN512VLH12 chip clocked by an 8MHz crystal oscillator. For my current application, I have an external 10MHz reference signal and 1PPS signal available from a GPS-disciplined clock. My current PCB is based on the design of the FRDM-K22 board and I am using the KDS + KSDK environment for firmware development. Is there a way to discipline the PLL on the Kinetis chip (the one which generates the main 80MHz or 120MHz clock) using the 10MHz reference so that the microcontroller belongs to the same clock domain.

If necessary, I can make quick connections to any required pins using wire wrap for testing out any solutions.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I am using KSDK V2.0 for FRDM-K22F software as an example, customer need to modify below codes:

1> <clock_config.h> file

line 36: #define BOARD_XTAL0_CLK_HZ 10000000U

2> <clock_config.c> file

//PLL refer clock is 2MHz with VDIV0(Multiply Factor) 40 to get PLL clock 80MHz

line 109: .enableMode = 0U, .prdiv = 0x4U, .vdiv = 0x10U,

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I am using KSDK V2.0 for FRDM-K22F software as an example, customer need to modify below codes:

1> <clock_config.h> file

line 36: #define BOARD_XTAL0_CLK_HZ 10000000U

2> <clock_config.c> file

//PLL refer clock is 2MHz with VDIV0(Multiply Factor) 40 to get PLL clock 80MHz

line 109: .enableMode = 0U, .prdiv = 0x4U, .vdiv = 0x10U,

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the quick and simple suggestion. I'll definitely try them out after a quick hardware patch-up.

It would also be very helpful if you could suggest the settings for 120MHz HS mode? This is the mode my processor primarily runs at.

Are there some features of the chip that may perform wrongly since I'm changing the input clock frequency? Based on the internal clock circuitry, I feel there shouldn't be any difference, but I'd just like to be sure in case other problems start to pop-up.

Lastly, do you know how fast of an input the XTAL0 line may accept? Could I feed it something as high as 48MHz (and correspondingly upscale it to 120MHz) which is being generated for use with another sensor.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

For 120MHz just set the PLL multiplication factor to 48 (2.5MHz x 48 = 120MHz) as well as setting HSRUN mode (beware fo HSRUN mode restrictions such as no Flash programming is possible).

The EXTAL input can accept up to 50MHz input frequencies.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Some general MCG details:

http://www.utasker.com/kinetis/MCG.html

If you use the 10MHz clock input on EXTAL you can use it as PLL reference to generate (for example) 80MHz system clock:

- configure for oscillator instead of crystal

- divide the 10MHz by 4 to 2.5MHz reference

- multiple by 32 for 80MHz

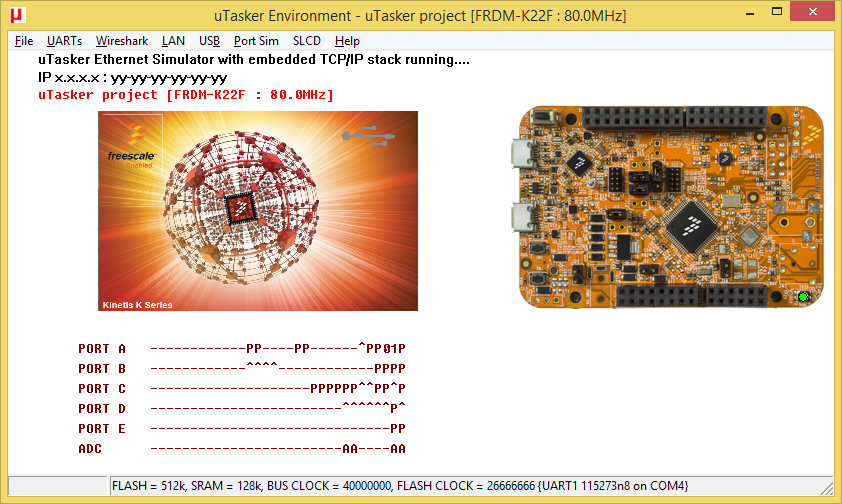

I don't know how it is done in KSDK but in the uTasker environment it is controlled by:

#define EXTERNAL_CLOCK 10000000 // 10MHz external oscillator (not crystal)

#define CLOCK_DIV 4 // input must be divided to 2MHz..4MHz range (/1 to /24)

#define CLOCK_MUL 32 // the PLL multiplication factor to achieve operating frequency of 80MHz (x24 to x55 possible)

Regards

Mark

Kinetis for professionals: http://www.utasker.com/kinetis.html