- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- KL03 rtc clock instable

KL03 rtc clock instable

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

KL03 rtc clock instable

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have developed a project with a MKL03Z32VFG4 with a 32768Hz crystal and powered by a 2045 coin battery.

The application uses only the RTC seconds counter and in normal run mode the clock remains always precise and correct. The mcu enters in VLSS0 easily and current is under 1uA; but when it exits from low power state the clock counter is incorrect and the seconds count can be a lesser or higher, without any apparent reason.

All the prototypes ( >10) we have tested present this problem. Do someone have an idea of where to look, hw? fw?

Thanks for any suggestion...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

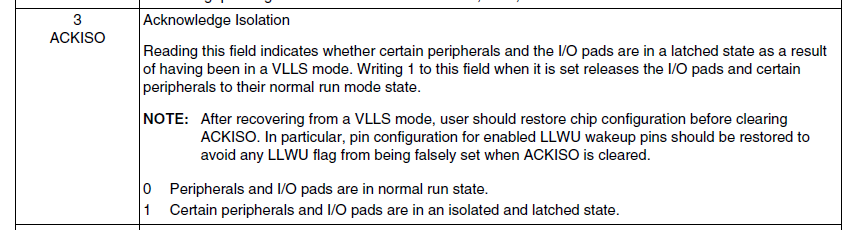

I would recommend customer to check whether I/O pads (XTAL/EXTAL) are not in latched state as dedicated after recovery from VLLS mode. Check ACKISO definition in PMC module chapter.

regards

R.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using KDS v3.2.0 and KSDK 1.3.0 with some PE components and in Events.c I have:

void LLWU_IRQHandler(void)

{

POWER_SYS_ClearAckIsolation();

POWER_SYS_ClearWakeupPinFlag(kPowerManagerWakeupPin4);

}

Is this not enough?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

well, it could depend on in what time the function is executed.

NOTE:

For LLWU Flag X registers:

- For LLS, this is the source causing the CPU interrupt flow. So, interrupt handler execution is expected.

- For VLLS, this is the source causing the MCU reset flow

I would expect that for VLLS0 mode you detect whether the reset was caused by LLWU wake up trought the system reset status registers.

regards

R.