- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Problem with disabling the MPLL

Problem with disabling the MPLL

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Problem with disabling the MPLL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When using a 26 MHz crystal, we can disable the MPLL to go to sleep mode. When the crystal is replaced with a 26 MHz oscillator, the MPLL is not reliably disabled.

The Reference manual states:

The conditions to be satisfied before the PLL Clock Controller actually turns off the MPLL are as

follows:

1. Clock Controller module has successfully mastered the system bus.

2. The A9P_CLK_OFF signal from the ARM9 Platform is active.

3. SDRAM controller has successfully placed the external SDRAM into Self-Refresh mode.

4. After the above conditions are satisfied, the countdown based on the value in the SD_CNT field

will be initiated.

5. SD_CNT countdown completes.

What could prevent the Clock Controller module from successfully mastering the system bus?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Craig

Clock Controller module may not successfully master the system bus

due to incorrect power-up sequence or external 26MHz clock noise /

noise on OSC26VDD, MPLLVDD power supplies. Note, external clock should

not be provided to unpowered processor, it should be applied along with

OSC26VDD power supply. In general one can check low power mode sequence

by oscillosope outputting MPLL clock on CLKO pin with CCSR register or

check CKE signal with Figure 18-37. SDRAM/LPDDR Enter Self Refresh Mode

During System Sleep Mode i.MX27 RM.

Datasheet on p.28 recommends to disable oscillator circuit with CSCR (OSC26M_DIS)

and apply clock to EXTAL26M. http://cache.freescale.com/files/dsp/doc/data_sheet/MCIMX27EC.pdf

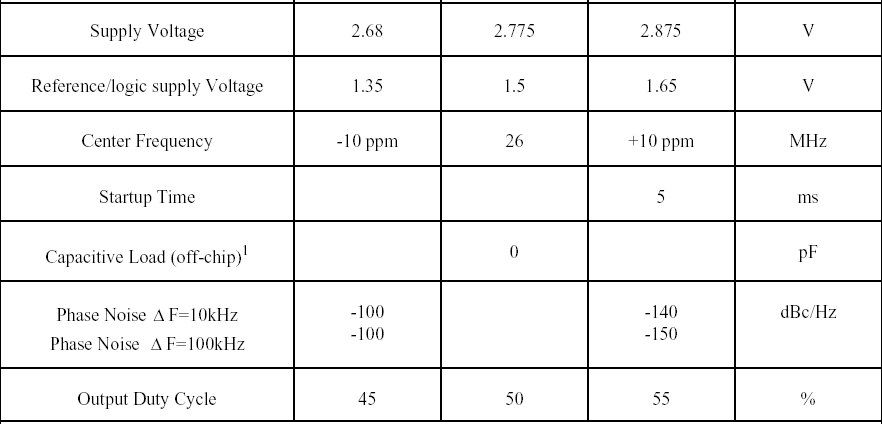

External clock may not have the desired spectral purity, only a crystal will provide the necessary signal quality.

Below oscillator specs

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Igor,

Thanks for the reply.

Where can I find a specification on spectral purity and noise for the 26MHz oscillator?

According to the reference manual it can be a square wave.

When I first started looking at replacing the crystal with an oscillator I could not find any requirements for the i.MX27. A FAE at Avnet said to use the i.MX25 requirements.

Also, with regards to disabling the oscillator, we have tried that and the system does not run. In an earlier post you said:

Hi Chris

this bit can disable internal schematic, related to input 26MHz clock.

OSC26M_DIS = 1 disable 26MHz clock at all. This may be needed, say,

to decrease consumption when 26MHz clock is not used.

So, for any 26MHz configuration (crystal or generator) OSC26M_DIS

should be cleared.

Best regards

igor

Craig

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Craig

please create service request for providing

additional documents.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How and where do I create a service request?

Craig

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

To submit case please follow below steps:

1) Go to http://www.nxp.com/support/sales-and-support:SUPPORTHOME.

2) On the bottom of the page under Submit New Issues, click Hardware & Software.

3) Register with your business email to access NXP technical online support.

4) A verification email will be sent to your account. Click the link embedded in that email to verify your access.

5) On the NXP online support page, select Contact Support from the top menu

and click ôsubmit a new caseö to start the process

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks.