- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Software Forums

- :

- Processor Expert Software

- :

- ADC Clock Divide Select from the register ADC0_CFG1.

ADC Clock Divide Select from the register ADC0_CFG1.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello all,

I have a FRDM-KL25Z and I am working with the ADC.

I configure the ADC_LDD component with the PE, to make it to work in continuous measuremente mode with interrupts. I save the results of the ADC conversions into an array.

The PE defines the Clock Divide Select bits from the ADC0_CFG1 register as input clock/2 (ADIV = 01) . However I am interested to make the conversiones as fast as possible, so I change the register value manualy to input clock/1 (ADIV = 00).

I use a led pin to see the time that needs 3000 measurements by the oscilloscope, and I see that there is no difference when I change ADIV to 00.

In both cases it need 7.13ms for 3000measuremente (2.37us per measure). How is that possible? Should not be a difference when the ADC clock is changed?

Please find below my code.

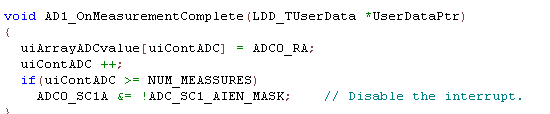

And this is the interrupt routine:

Thank you in advance. Any help will be appreciated.

Aitor.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The problem is caused by the high ADC clock frequency. There is defined a limit frequency that depend on the selected configuration of the ADC device, see for example KL25Z datasheet:

There is following table:

When you set higher ADC clock frequency the behavior of the ADC device is not defined (I have already checked on the FRDM-KL2Z target board).

You can enable High-speed conversion mode, 8-bits A/D resolution and shortest sample time to achieve the fastest conversion time. See also the KL25Z reference manual for details about the ADC conversion time.

Best Regards,

Marek Neuzil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Marek,

BR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The problem is caused by the high ADC clock frequency. There is defined a limit frequency that depend on the selected configuration of the ADC device, see for example KL25Z datasheet:

There is following table:

When you set higher ADC clock frequency the behavior of the ADC device is not defined (I have already checked on the FRDM-KL2Z target board).

You can enable High-speed conversion mode, 8-bits A/D resolution and shortest sample time to achieve the fastest conversion time. See also the KL25Z reference manual for details about the ADC conversion time.

Best Regards,

Marek Neuzil