- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Problem with address bit 13 when accessing MRAM on TWRMEM module

Problem with address bit 13 when accessing MRAM on TWRMEM module

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’ve encountered an issue with the MRAM access when running a memory device test.

I’ve purchased three tower boards – the main board, the serial communication board (TWRSER) and the memory board (TWRMEM). I put the three boards together and run a memory test code on the MRAM through flexbus (print out the result on UART3). I followed the flexbus configuration and MRAM access code from AN4393. When I run the memory write and read-back test, all memory location on the MRAM runs fine except when bit 13 of the address line is high. Any location with address bit 13 high always read back a value of 0xAD. (Anything in the range of X2XXX to X3XXX, X6XXX to X7XXX, XAXXX to XBXXX, XEXXX to XFXXX).

From the pattern of the error, it would look like bit 13 of the address bus (PTC1) is triggering something that cause the data bus to go 0xAD?

Here are the versions of boards and the jumper setting that I’m using:

Mainboard: 700-26548 REV E (I'm using TWN-K60N512)

J1 ON, J6 1-2, J8 ON, J9 1-2, J12 ON

TWR-MRM: 700-26248 REV A

J1 1-2, J3 1-2, J4 1-2, J10 ON, J12 1-2, J13 ON, J14 1-2, J15 ON, J16 2-3

TWR-SER: 700-26004 REV E

J2 1-2, J15 1-2, J16 1-2, J17 1-2, J19 1-2

Here are the flexbus configuration that I use (same as AN4393):

#define MRAM_CSAR_BA (*(UTiny*)(0x60000000)) /* Chip Select Address for MRAM - use non-cacheable region*/

#define MRAM_CS (0) /* Chip Select index for MRAM peripheral */

#define MRAM_CSMR_BAM (0x07) /* Base Address Mask for MRAM. 0x07 represent a memory range of 512kb */

#define MRAM_CSMR_WP (0)

#define MRAM_CSMR_V (1) /* CSAR, CSMR and CSCR are valid */

#define MRAM_CSCR_SWS (0)

#define MRAM_CSCR_SWSEN (0)

#define MRAM_CSCR_EXTS (0)

#define MRAM_CSCR_ASET (1)

#define MRAM_CSCR_RDAH (0)

#define MRAM_CSCR_WRAH (0)

#define MRAM_CSCR_WS (1) /* Wait state is 1 */

#define MRAM_CSCR_BLS (1)

#define MRAM_CSCR_AA (1) /* Automatic Acknowledge enabled */

#define MRAM_CSCR_PS (1) /* Port size is 8 bit */

#define MRAM_CSCR_BEM (0)

#define MRAM_CSCR_BSTR (0)

#define MRAM_CSCR_BSTW (0)

Here are part of the memory test result:

Address bus test begin...Write 00000055 to power of 2 addresses.

00000001 passed. W:00000055 R:00000055

00000002 passed. W:00000055 R:00000055

00000004 passed. W:00000055 R:00000055

00000008 passed. W:00000055 R:00000055

00000010 passed. W:00000055 R:00000055

00000020 passed. W:00000055 R:00000055

00000040 passed. W:00000055 R:00000055

00000080 passed. W:00000055 R:00000055

00000100 passed. W:00000055 R:00000055

00000200 passed. W:00000055 R:00000055

00000400 passed. W:00000055 R:00000055

00000800 passed. W:00000055 R:00000055

00001000 passed. W:00000055 R:00000055

00002000 failed. W:00000055 R:000000AD

00004000 passed. W:00000055 R:00000055

00008000 passed. W:00000055 R:00000055

00010000 passed. W:00000055 R:00000055

00020000 passed. W:00000055 R:00000055

00040000 passed. W:00000055 R:00000055

I’ve also run another memory test with bit 13 low all the time – and all other memory location passed the write-readback test.

The TWRMEM's new and I doubt it is faulty. Could there be jumper setting that I'm not aware of? Conflicts between the three boards? or something in the software setting (not mentioned in AN4393)?

Thank you for your help!

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, jacky,

I think it is MRAM issue instead of Kinetis. I can duplicate your issue with freescale demo code. The following is the results:

I suggest you ask the manufacturer of MRAM.

BR

XiangJun Rong

Demo code outputs:

"

External Pin Reset

K60-144pin

rev 0

Full size P-flash 128 kBytes of RAM

****MRAM Test****

Initializing the FlexBus

FB_CSCR0 is 00100540

FB_CSMR0 is 00070001

FB_CSAR0 is 60000000

FB_CSPMCR is 02200000

SIM_CLKDIV1 is 01330000

Testing 8-bit write/reads

ADDR: 0x60002000 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002001 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002002 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002003 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002004 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002005 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002006 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002007 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002008 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002009 WRITE: 0xA5 READ: 0xAD

ADDR: 0x6000200A WRITE: 0xA5 READ: 0xAD

ADDR: 0x6000200B WRITE: 0xA5 READ: 0xAD

ADDR: 0x6000200C WRITE: 0xA5 READ: 0xAD

ADDR: 0x6000200D WRITE: 0xA5 READ: 0xAD

ADDR: 0x6000200E WRITE: 0xA5 READ: 0xAD

Testing 16-bit write/reads

ADDR: 0x60002010 WRITE: 0x1234 READ: 0xADAD

ADDR: 0x60002012 WRITE: 0x1234 READ: 0xADAD

ADDR: 0x60002014 WRITE: 0x1234 READ: 0xADAD

ADDR: 0x60002016 WRITE: 0x1234 READ: 0xADAD

ADDR: 0x60002018 WRITE: 0x1234 READ: 0xADAD

ADDR: 0x6000201A WRITE: 0x1234 READ: 0xADAD

ADDR: 0x6000201C WRITE: 0x1234 READ: 0xADAD

ADDR: 0x6000201E WRITE: 0x1234 READ: 0xADAD

"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Jacky,

Frankly speaking, I have not good idea how to explain your phenomenon. Even if the A13 is wrong for example the the FlexBus does not drive A13 pin because of incorrect configuration, if you write the data to MRAM, then read it back immediately, the reading data should be correct if the A13 logic can keep constant in the writing/reading process.

In your code, you can write/read the 0x200 address in a forever loop, connect the FB_A13 to scope, check it's timing, you can connect the FB_A13 pin out via the A67/A40 on the Primary elevator board. Note FB_A13 is multiplexed with FTM0_CH0 pin.

BTW, if you write/read all address from 0x2000 to 0x2FFF, what is the result?

If you still have issue, pls attach your code, we can test on our board.

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Xiangjun,

Thank you for the suggestions. Here are the checks that I've made:

Any address with bit 13 high result in reading 0xAD, that includes from 0x2000 to 0x2FFF. (thus any location in X2XXX to X3XXX, X6XXX to X7XXX, XAXXX to XBXXX, XEXXX to XFXXX). Any other address are working correctly.

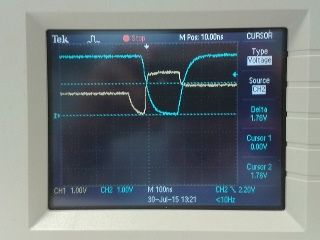

Using a scope, I've found the following.

1. FB_A13 (via A67) is behaving correctly.

2. Writing to Address location 0x2000 is behaving correctly - I've scoped the CS (via B64) with each of the data pin (via B80 to B73). All logic's working correctly.

3. Reading Address location 0x2000 is bad - the behavior of the address pin's fine - Address pin shows the value 0x2000. Data pin is showing strange values: The pin's driving to some "in-between" values:

B73 (D7): 2.36V (H)

B74 (D6): 0.96V (L)

B75 (D5): 1.76V (H)

B76 (D4): 0.96V (L)

B77 (D3): 2.36V (H)

B78 (D2): 1.76V (H)

B79 (D1): 0.96V (L)

B80 (D0): 2.36V (H)

The value agrees with what the flexbus read: 0xAD, so flexbus sampling is correct, but the signal driven on the flexbus by the MRAM is not right.

I've attached the main program I use to obtain these values, and the scope image of the signal line.

Above is the signal I saw - blue being the CS, yellow is B80 (D0).

Below is the main program:

// Sample code to read and write MRAM

/***************************************************************************************************

* -- FB Peripheral Access Layer

***************************************************************************************************/

#include "system.h"

#include "gpio.h"

#include <stdio.h>

/**

* @addtogroup FB_Peripheral_Access_Layer FB Peripheral Access Layer

* @{

*/

#define NB_CS_REGISTER_IN_STRUCT_FB (6)

#define NB_RESERVED_0_BYTES_IN_STRUCT_FB (24)

/** FB - Register Layout Typedef */

typedef struct

{

struct

{ /* offset: 0x0, array step: 0xC */

VOLATILE_INPUT_OUTPUT ULong CSAR; /**< Chip select address register, array offset: 0x0, array step: 0xC */

VOLATILE_INPUT_OUTPUT ULong CSMR; /**< Chip select mask register, array offset: 0x4, array step: 0xC */

VOLATILE_INPUT_OUTPUT ULong CSCR; /**< Chip select control register, array offset: 0x8, array step: 0xC */

} CS[NB_CS_REGISTER_IN_STRUCT_FB];

UTiny RESERVED_0[NB_RESERVED_0_BYTES_IN_STRUCT_FB];

VOLATILE_INPUT_OUTPUT ULong CSPMCR; /**< Chip select port multiplexing control register, offset: 0x60 */

} FB_Type;

/* ----------------------------------------------------------------------------

-- FB Register Masks

---------------------------------------------------------------------------- */

/**

* @addtogroup FB_Register_Masks FB Register Masks

* @{

*/

/* CSAR Bit Fields */

#define FB_CSAR_BA_MASK (0xFFFF0000u)

#define FB_CSAR_BA_SHIFT (16)

#define FB_CSAR_BA(x) (((ULong)(((ULong)(x))<<FB_CSAR_BA_SHIFT))&FB_CSAR_BA_MASK)

/* CSMR Bit Fields */

#define FB_CSMR_V_MASK (0x1u)

#define FB_CSMR_V_SHIFT (0)

#define FB_CSMR_WP_MASK (0x100u)

#define FB_CSMR_WP_SHIFT (8)

#define FB_CSMR_BAM_MASK (0xFFFF0000u)

#define FB_CSMR_BAM_SHIFT (16)

#define FB_CSMR_BAM(x) (((ULong)(((ULong)(x))<<FB_CSMR_BAM_SHIFT))&FB_CSMR_BAM_MASK)

/* CSCR Bit Fields */

#define FB_CSCR_BSTW_MASK (0x8u)

#define FB_CSCR_BSTW_SHIFT (3)

#define FB_CSCR_BSTR_MASK (0x10u)

#define FB_CSCR_BSTR_SHIFT (4)

#define FB_CSCR_BEM_MASK (0x20u)

#define FB_CSCR_BEM_SHIFT (5)

#define FB_CSCR_PS_MASK (0xC0u)

#define FB_CSCR_PS_SHIFT (6)

#define FB_CSCR_PS(x) (((ULong)(((ULong)(x))<<FB_CSCR_PS_SHIFT))&FB_CSCR_PS_MASK)

#define FB_CSCR_AA_MASK (0x100u)

#define FB_CSCR_AA_SHIFT (8)

#define FB_CSCR_BLS_MASK (0x200u)

#define FB_CSCR_BLS_SHIFT (9)

#define FB_CSCR_WS_MASK (0xFC00u)

#define FB_CSCR_WS_SHIFT (10)

#define FB_CSCR_WS(x) (((ULong)(((ULong)(x))<<FB_CSCR_WS_SHIFT))&FB_CSCR_WS_MASK)

#define FB_CSCR_WRAH_MASK (0x30000u)

#define FB_CSCR_WRAH_SHIFT (16)

#define FB_CSCR_WRAH(x) (((ULong)(((ULong)(x))<<FB_CSCR_WRAH_SHIFT))&FB_CSCR_WRAH_MASK)

#define FB_CSCR_RDAH_MASK (0xC0000u)

#define FB_CSCR_RDAH_SHIFT (18)

#define FB_CSCR_RDAH(x) (((ULong)(((ULong)(x))<<FB_CSCR_RDAH_SHIFT))&FB_CSCR_RDAH_MASK)

#define FB_CSCR_ASET_MASK (0x300000u)

#define FB_CSCR_ASET_SHIFT (20)

#define FB_CSCR_ASET(x) (((ULong)(((ULong)(x))<<FB_CSCR_ASET_SHIFT))&FB_CSCR_ASET_MASK)

#define FB_CSCR_EXALE_MASK (0x400000u)

#define FB_CSCR_EXALE_SHIFT (22)

#define FB_CSCR_SWSEN_MASK (0x800000u)

#define FB_CSCR_SWSEN_SHIFT (23)

#define FB_CSCR_SWS_MASK (0xFC000000u)

#define FB_CSCR_SWS_SHIFT (26)

#define FB_CSCR_SWS(x) (((ULong)(((ULong)(x))<<FB_CSCR_SWS_SHIFT))&FB_CSCR_SWS_MASK)

/* CSPMCR Bit Fields */

#define FB_CSPMCR_GROUP5_MASK (0xF000u)

#define FB_CSPMCR_GROUP5_SHIFT (12)

#define FB_CSPMCR_GROUP5(x) (((ULong)(((ULong)(x))<<FB_CSPMCR_GROUP5_SHIFT))&FB_CSPMCR_GROUP5_MASK)

#define FB_CSPMCR_GROUP4_MASK (0xF0000u)

#define FB_CSPMCR_GROUP4_SHIFT (16)

#define FB_CSPMCR_GROUP4(x) (((ULong)(((ULong)(x))<<FB_CSPMCR_GROUP4_SHIFT))&FB_CSPMCR_GROUP4_MASK)

#define FB_CSPMCR_GROUP3_MASK (0xF00000u)

#define FB_CSPMCR_GROUP3_SHIFT (20)

#define FB_CSPMCR_GROUP3(x) (((ULong)(((ULong)(x))<<FB_CSPMCR_GROUP3_SHIFT))&FB_CSPMCR_GROUP3_MASK)

#define FB_CSPMCR_GROUP2_MASK (0xF000000u)

#define FB_CSPMCR_GROUP2_SHIFT (24)

#define FB_CSPMCR_GROUP2(x) (((ULong)(((ULong)(x))<<FB_CSPMCR_GROUP2_SHIFT))&FB_CSPMCR_GROUP2_MASK)

#define FB_CSPMCR_GROUP1_MASK (0xF0000000u)

#define FB_CSPMCR_GROUP1_SHIFT (28)

#define FB_CSPMCR_GROUP1(x) (((ULong)(((ULong)(x))<<FB_CSPMCR_GROUP1_SHIFT))&FB_CSPMCR_GROUP1_MASK)

/**

* @}

*/ /* end of group FB_Register_Masks */

/* FB - Peripheral instance base addresses */

/** Peripheral FB base address */

#define FB_BASE (0x4000C000u)

/** Peripheral FB base pointer */

#define FB ((FB_Type *)FB_BASE)

/** Array initializer of FB peripheral base pointers */

#define FB_BASES { FB }

/***************************************************************************************************

****************************************************************************************************

* Public operation declarations

****************************************************************************************************

***************************************************************************************************/

#if defined (K60TWR)

#define FB_NB_OF_DEVICE (1)

#elif defined (K61CPU)

#define FB_NB_OF_DEVICE (4)

#elif defined (K61OTP)

#define FB_NB_OF_DEVICE (6)

#endif

#define MRAM_CSAR_BA (*(unsigned char*)(0x60000000)) /* Chip Select Address for MRAM - use non-cacheable region*/

#define MRAM_CS (0) /* Chip Select index for MRAM peripheral */

#define MRAM_CSMR_BAM (0x07) /* Base Address Mask for MRAM. 0x07 represent a memory range of 512kb */

#define MRAM_CSMR_WP (0)

#define MRAM_CSMR_V (1) /* CSAR, CSMR and CSCR are valid */

#define MRAM_CSCR_SWS (0)

#define MRAM_CSCR_SWSEN (0)

#define MRAM_CSCR_EXTS (0)

#define MRAM_CSCR_ASET (1)

#define MRAM_CSCR_RDAH (0)

#define MRAM_CSCR_WRAH (0)

#define MRAM_CSCR_WS (4) /* Wait state is 1 */

#define MRAM_CSCR_BLS (1)

#define MRAM_CSCR_AA (1) /* Automatic Acknowledge enabled */

#define MRAM_CSCR_PS (1) /* Port size is 8 bit */

#define MRAM_CSCR_BEM (0)

#define MRAM_CSCR_BSTR (0)

#define MRAM_CSCR_BSTW (0)

#define MRAM_CSCR (FB_CSCR_WS(MRAM_CSCR_WS) | FB_CSCR_AA_MASK | FB_CSCR_PS(MRAM_CSCR_PS) | FB_CSCR_ASET(MRAM_CSCR_ASET)) /* auto-acknowledge and Port size is 16 bit */

#define MRAM_CSMR (FB_CSMR_BAM(MRAM_CSMR_BAM) | FB_CSMR_V_MASK) /* Set base address mask for 512kb address space and Enable cs signal*/

int main()

{

ULong usData;

unsigned char rVal = 0;

SIM->sCGC5 |= (SIM_SCGC5_PORTA_MASK | SIM_SCGC5_PORTB_MASK | SIM_SCGC5_PORTC_MASK |

SIM_SCGC5_PORTD_MASK | SIM_SCGC5_PORTE_MASK);

// initialize Flexbus

FB->CSPMCR = 0x00000;

FB->CSPMCR |= (0x02200000);

// K60 Tower board has a different set of pinouts

PORTB->pCR[11] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[18]

PORTB->pCR[16] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[17]

PORTB->pCR[17] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[16]

PORTB->pCR[18] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[15]

PORTC->pCR[0] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[14]

PORTC->pCR[1] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[13]

PORTC->pCR[2] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[12]

PORTC->pCR[4] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[11]

PORTC->pCR[5] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[10]

PORTC->pCR[6] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[9]

PORTC->pCR[7] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[8]

PORTC->pCR[8] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[7]

PORTC->pCR[9] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[6]

PORTC->pCR[10] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[5]

PORTD->pCR[2] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[4]

PORTD->pCR[3] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[3]

PORTD->pCR[4] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[2]

PORTD->pCR[5] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[1]

PORTD->pCR[6] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[0]

PORTB->pCR[20] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[31] used as d[7]

PORTB->pCR[21] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[30] used as d[6]

PORTB->pCR[22] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[29] used as d[5]

PORTB->pCR[23] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[28] used as d[4]

PORTC->pCR[12] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[27] used as d[3]

PORTC->pCR[13] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[26] used as d[2]

PORTC->pCR[14] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[25] used as d[1]

PORTC->pCR[15] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ad[24] used as d[0]

PORTB->pCR[19] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_oe_b

PORTC->pCR[3] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_clk

PORTC->pCR[11] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_rw_b

PORTD->pCR[1] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_cs0_b

PORTD->pCR[0] = PORT_PCR_MUX(PORT_PCR_MUX_FIVE); // fb_ale

FB->CS[MRAM_CS].CSAR = (ULong)&MRAM_CSAR_BA;

FB->CS[MRAM_CS].CSCR = MRAM_CSCR;

FB->CS[MRAM_CS].CSMR = MRAM_CSMR;

*(unsigned char*)(&(MRAM_CSAR_BA) + 0x02000) = 0x052;

/* Wait then look again. */

for (usData = 0; usData < 1000; usData++)

{

__asm( "NOP" );

}

while (1)

{

// *(unsigned char*)(&(MRAM_CSAR_BA) + 0x02000) = 0x052;

// /* Wait then look again. */

// for (usData = 0; usData < 1000; usData++)

// {

// __asm( "NOP" );

// }

rVal = (*(unsigned char*)(&MRAM_CSAR_BA + 0x02000));

rVal++;

/* Wait then look again. */

for (usData = 0; usData < 1000; usData++)

{

__asm( "NOP" );

}

}

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, jacky,

I think it is MRAM issue instead of Kinetis. I can duplicate your issue with freescale demo code. The following is the results:

I suggest you ask the manufacturer of MRAM.

BR

XiangJun Rong

Demo code outputs:

"

External Pin Reset

K60-144pin

rev 0

Full size P-flash 128 kBytes of RAM

****MRAM Test****

Initializing the FlexBus

FB_CSCR0 is 00100540

FB_CSMR0 is 00070001

FB_CSAR0 is 60000000

FB_CSPMCR is 02200000

SIM_CLKDIV1 is 01330000

Testing 8-bit write/reads

ADDR: 0x60002000 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002001 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002002 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002003 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002004 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002005 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002006 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002007 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002008 WRITE: 0xA5 READ: 0xAD

ADDR: 0x60002009 WRITE: 0xA5 READ: 0xAD

ADDR: 0x6000200A WRITE: 0xA5 READ: 0xAD

ADDR: 0x6000200B WRITE: 0xA5 READ: 0xAD

ADDR: 0x6000200C WRITE: 0xA5 READ: 0xAD

ADDR: 0x6000200D WRITE: 0xA5 READ: 0xAD

ADDR: 0x6000200E WRITE: 0xA5 READ: 0xAD

Testing 16-bit write/reads

ADDR: 0x60002010 WRITE: 0x1234 READ: 0xADAD

ADDR: 0x60002012 WRITE: 0x1234 READ: 0xADAD

ADDR: 0x60002014 WRITE: 0x1234 READ: 0xADAD

ADDR: 0x60002016 WRITE: 0x1234 READ: 0xADAD

ADDR: 0x60002018 WRITE: 0x1234 READ: 0xADAD

ADDR: 0x6000201A WRITE: 0x1234 READ: 0xADAD

ADDR: 0x6000201C WRITE: 0x1234 READ: 0xADAD

ADDR: 0x6000201E WRITE: 0x1234 READ: 0xADAD

"