- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: Testing CM4 core in MIMXRT1176

Testing CM4 core in MIMXRT1176

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Testing CM4 core in MIMXRT1176

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm working with RT-1176 custom designed board. I had few queries regarding core CM7/CM4

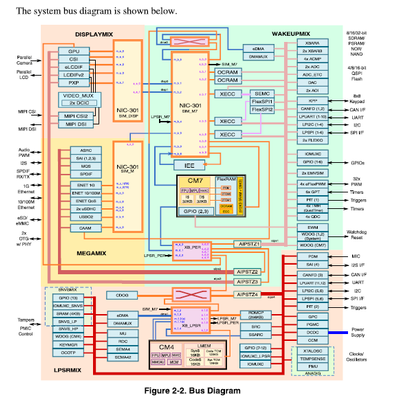

1)In reference manual, the below block diagram show the peripherals dedicated to CM7 and CM4.

Consider LPI2C5 belongs to CM4, but I created a project selecting core CM7 and started testing salve connected to LPI2C5, as per my understanding it belongs to CM4 but why it is working with CM7.

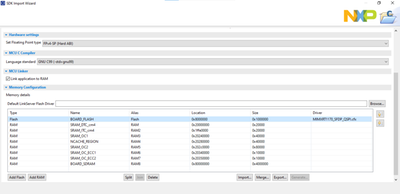

2)When I imported SDK example for CM4 then in Memory Configuration:

"LINK TO RAM" is enabled and memory it is mapping to 0x8000_0000.

why? Is it designed such a way that CM7 only able to access QSPI (0X3000_0000).

And How to Flash Projects belongs to CM4 using J-link(Is the process same as CM7 instead of connecting CM7 we need to Connect--->Device MIMXRT1176XXX_CM4. Awaiting for reply.

Thanks & Regards,

Manikanta Robbi.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ManikantaRobbi,

- Both cores can access all peripherals. But the access to the dedicated peripherals is faster and does not add load on the crossbar of the other core.

- The Memory mapped access to the external Flash via FlexSPI is available on two address ranges for the M4-Core. 0x0800_0000 is faster for code execution for the M4 core.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Masmiseim ,

Thanks for the information. But why we need to perform testing CM4 using "LINK TO RAM" only in EVK.

Cant we flash to QSPI.

Thanks & Regards,

Manikanta Robbi.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @ManikantaRobbi ,

that depends on how you want to start the M4 core. By default, the M7 core is the master core. This means that only this core starts after the operating voltage is applied. At runtime, the M7 core can then start the M4 core

In the SDK examples, the M4 core is linked to the RAM area. The M7 core then loads the memory area (with code and data) into the RAM and starts the M4 core with the RAM area as the start address.

Alternatively, you can also link the M4 core into the flash; in this case you must ensure that the two images (for the M7 and M4 core) do not overlap, i.e. that they are in separate "partitions". The M4 can then be started with the address of the flash partition (XiP). The start address is then in the 0x3000_0000 range, even if the M4 application is linked to 0x0800_0000.

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @Masmiseim ,

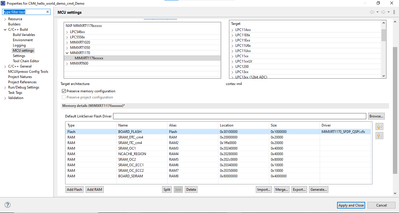

This information is useful, I had approached same way creating a new project for CM4 and Disabled "LINK TO RAM" and changed default mem config. As you mentioned we can use CM4 to flash in 0x30000000 region. Can you elaborate procedure during mem config, I tried many possible case all builds are getting failed.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How this is done depends on the Development Environment. I guess you are using MCUXpresso, but I’m not familiar with this IDE.

But basically, the configuration should be identical to the one from the M7 core with the exception of the “.boot_xxx” sections. These sections are only necessary on the M4 core.

And of course, the Flash Base-Address must be different to avoid a overlapping of the image from both cores.

For example:

0x30000000 --> M7-Core with one Megabyte Flash-Space

0x30100000 --> M4-Core respectively 0x08100000

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Masmiseim ,

Thanks for the information. I had followed the instructions for mem config. Image attached reflects the changes done in memory "0x30100000" and the project created for CM4. But again I'm getting build failed.

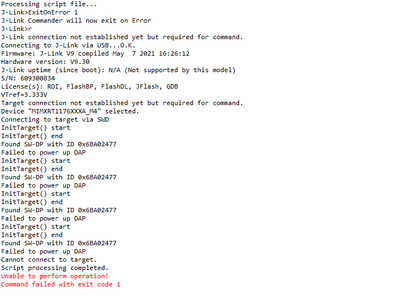

This is log message after build.

So can't we create a new project for CM4 access the QSPI.

Thanks,

Manikanta Robbi.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Looks to me like a problem with the JTAG connection. Does a connect via J-Link Commander to the M4 core of the iMXRT1170 work?