- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: MIMXRT1061 dual SDRAM

MIMXRT1061 dual SDRAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

(related to: https://community.nxp.com/t5/i-MX-RT/imxrt1062-and-dual-SDRAM-IC-s/td-p/1133053)

I would like to connect two 16bit SDRAMs in parallel on the 16bit SEMC databus on MIMXRT1061DVJ6B.

As described in the post, referred to at the top, I should connect all signals in parallel except for the chip selects correct?

Unfortunately I could not find any reference design where this is used.. Only following application note for LPCx where this parallel setup is described (section 2.3.2): https://www.nxp.com/docs/en/application-note/AN11508.pdf

In the figure, indeed, all signals are connected in parallel except for the chip selects, but also the clock (CLK) and clock enable (CKE) are seperate for each SDRAM.

When looking through the MIMXRT1061 reference manual and pinmux tool, I can only find one clock (SEMC_CLK) and one enable (SEMC_CKE) pin..

My question:

Can we connect two SDRAMS in parallel as described in the application note figure 10, and use a single clock (SEMC_CLK) and clock enable (SEMC_CKE) for both the SDRAMs?

If you have a reference design or guidelines, feel free to refer to those as well.

Thanks in advance,

Gert

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

Hope you are well.

You are correct! If multiple SDRAMS are connected they share the signals except for the CS. CKE and CLK pins are also shared.

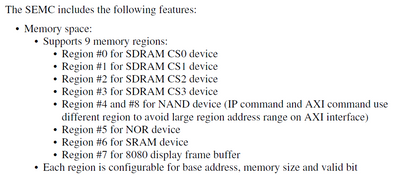

Each CS has an specific region, each region specifies the base address and memory size through BRn register.

Unfortunately, we don´t have an specific reference design to connect multiple SDRAMs.

If you have more questions do not hesitate to ask me.

Best regards,

Omar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

Hope you are well.

You are correct! If multiple SDRAMS are connected they share the signals except for the CS. CKE and CLK pins are also shared.

Each CS has an specific region, each region specifies the base address and memory size through BRn register.

Unfortunately, we don´t have an specific reference design to connect multiple SDRAMs.

If you have more questions do not hesitate to ask me.

Best regards,

Omar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Omar_Anguiano ,

I will have dual SDRAMs on my customize board. The CS pin of one of them is connected to IOMUXC_GPIO_EMC_29_SEMC_CS0, and the other one is connected to IOMUXC_GPIO_B0_02_SEMC_CSX03.

status_t BOARD_InitSEMC(void)

{

semc_config_t config;

semc_sdram_config_t sdramconfig;

semc_sdram_config_t sdramconfig_second_sdram;

uint32_t clockFrq = EXAMPLE_SEMC_CLK_FREQ;

printf("clockFrq:%ld (0x%x)\n",clockFrq,clockFrq);

/* Initializes the MAC configure structure to zero. */

memset(&config, 0, sizeof(semc_config_t));

memset(&sdramconfig, 0, sizeof(semc_sdram_config_t));

memset(&sdramconfig_second_sdram, 0, sizeof(semc_sdram_config_t));

/* Initialize SEMC. */

SEMC_GetDefaultConfig(&config);

config.dqsMode = kSEMC_Loopbackdqspad; /* For more accurate timing. */

SEMC_Init(SEMC, &config);

/* Configure SDRAM1. */

sdramconfig.csxPinMux = kSEMC_MUXCSX0;

sdramconfig.address = 0x80000000;

sdramconfig.memsize_kbytes = 128 * 1024; /* 16MB = 16*1024*1KBytes*/

sdramconfig.portSize = kSEMC_PortSize16Bit;

sdramconfig.burstLen = kSEMC_Sdram_BurstLen8;

sdramconfig.columnAddrBitNum = kSEMC_SdramColunm_9bit;

sdramconfig.casLatency = kSEMC_LatencyThree;

sdramconfig.tPrecharge2Act_Ns = 18; /* Trp 18ns */

sdramconfig.tAct2ReadWrite_Ns = 18; /* Trcd 18ns */

sdramconfig.tRefreshRecovery_Ns = 72; /* Use the maximum of the (Trfc , Txsr). */

sdramconfig.tWriteRecovery_Ns = 18; /* 12ns */

sdramconfig.tCkeOff_Ns =

42; /* The minimum cycle of SDRAM CLK off state. CKE is off in self refresh at a minimum period tRAS.*/

sdramconfig.tAct2Prechage_Ns = 42; /* Tras 42ns */

sdramconfig.tSelfRefRecovery_Ns = 72;

sdramconfig.tRefresh2Refresh_Ns = 60;

sdramconfig.tAct2Act_Ns = 60;

sdramconfig.tPrescalePeriod_Ns = 160 * (1000000000 / clockFrq);

sdramconfig.refreshPeriod_nsPerRow = 64 * 1000000 / 8192; /* 64ms/8192 */

sdramconfig.refreshUrgThreshold = sdramconfig.refreshPeriod_nsPerRow;

sdramconfig.refreshBurstLen = 1;

if (SEMC_ConfigureSDRAM(SEMC, kSEMC_SDRAM_CS0, &sdramconfig, clockFrq) != kStatus_Success)

{

printf("\r\n The first SDRAM init failed ! \r\n");

return kStatus_Fail;

}

/* Configure SDRAM2. */

sdramconfig_second_sdram.csxPinMux = kSEMC_MUXCSX3;

sdramconfig_second_sdram.address = 0x88000000;

sdramconfig_second_sdram.memsize_kbytes = 128 * 1024; /* 16MB = 16*1024*1KBytes*/

sdramconfig_second_sdram.portSize = kSEMC_PortSize16Bit;

sdramconfig_second_sdram.burstLen = kSEMC_Sdram_BurstLen8;

sdramconfig_second_sdram.columnAddrBitNum = kSEMC_SdramColunm_9bit;

sdramconfig_second_sdram.casLatency = kSEMC_LatencyThree;

sdramconfig_second_sdram.tPrecharge2Act_Ns = 18; /* Trp 18ns */

sdramconfig_second_sdram.tAct2ReadWrite_Ns = 18; /* Trcd 18ns */

sdramconfig_second_sdram.tRefreshRecovery_Ns = 72; /* Use the maximum of the (Trfc , Txsr). */

sdramconfig_second_sdram.tWriteRecovery_Ns = 18; /* 12ns */

sdramconfig_second_sdram.tCkeOff_Ns =

42; /* The minimum cycle of SDRAM CLK off state. CKE is off in self refresh at a minimum period tRAS.*/

sdramconfig_second_sdram.tAct2Prechage_Ns = 42; /* Tras 42ns */

sdramconfig_second_sdram.tSelfRefRecovery_Ns = 72;

sdramconfig_second_sdram.tRefresh2Refresh_Ns = 60;

sdramconfig_second_sdram.tAct2Act_Ns = 60;

sdramconfig_second_sdram.tPrescalePeriod_Ns = 160 * (1000000000 / clockFrq);

sdramconfig_second_sdram.refreshPeriod_nsPerRow = 64 * 1000000 / 8192; /* 64ms/8192 */

sdramconfig_second_sdram.refreshUrgThreshold = sdramconfig_second_sdram.refreshPeriod_nsPerRow;

sdramconfig_second_sdram.refreshBurstLen = 1;

return SEMC_ConfigureSDRAM(SEMC, kSEMC_SDRAM_CS3, &sdramconfig_second_sdram, clockFrq);

}