- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: i.MX8MQ <-> i.MX8MQ RGMII link is not working at (1G) speed in custom board (100M is worki

i.MX8MQ <-> i.MX8MQ RGMII link is not working at (1G) speed in custom board (100M is working)

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi NXP Team,

We are working on the RGMII <> RGMII communication between two i.MX8MQ processor. 100 speed between two processors are working fine, however, 1000 is not working well.

- Same connections as we have mentioned in this thread. (https://community.nxp.com/t5/i-MX-Processors/iMX8-MAC-to-MAC-comm/m-p/1076188#M157972)

- Attached is the Signal net-length report (All signals are within 20 mil wrt clock)

- We have performed signal integrity analysis too on this RGMII interface.

- Using standard fixed-phy driver

- Attached is the 100(100M) configurations which are working fine. (Checked by ping, iperf, and scp between both the processors)

- Attached is the DTS configuration for the 1000 (1G) which is not working. Please note that we have probed and confirmed that we are getting a proper clock of 125MHz.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi harshitshah,

We asked our design team regarding the support or workaround for adding a delay in the RXC/TXC in i.MX8MQ, but it seems it is not supported in the SoC.

It supports only:

- RGMII TX no delay@1.8V

- RGMII RX no delay@1.8V

and do not support:

- RGMII RX delay

- RGMII TX delay

So the software delay is not supported in i.MX8MQ support.

Regards,

Karan Gajjar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

@shivani_patel can you help to continue with the follow up?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi harshitshah,

We asked our design team regarding the support or workaround for adding a delay in the RXC/TXC in i.MX8MQ, but it seems it is not supported in the SoC.

It supports only:

- RGMII TX no delay@1.8V

- RGMII RX no delay@1.8V

and do not support:

- RGMII RX delay

- RGMII TX delay

So the software delay is not supported in i.MX8MQ support.

Regards,

Karan Gajjar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you @nxf65420 and NXP team,

We will move forward with the layout changes for adding a delay as there is no such register on the chipset.

Regards.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

This is not the ping issue.

1g is working by adding the 3-inch cable in hardware clock lines (tx & rx) channels. (On PCB for MAC <-> MAC communication we have already matched the data signals wrt clock within a 20 mils, the clock is higher than data).

1) In TRM there are no registers to adjust the clock skew on the MAC receive and transmit blocks.

Can you please let us know where we will get the register for setting up the skew register in i.MX8MQ from the software.

Regards.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi harshitshah

unfortunately i.MX8MQ does not support skew programming.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

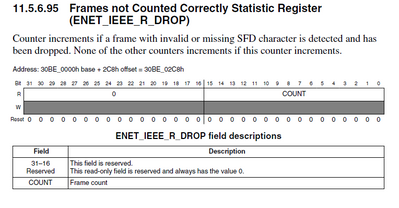

In this case, the 100M is working fine but 1g is not working (We have connected the MAC to MAC directly between two processors). The error we are getting here the ENET_IEEE_R_DROP packets with 1g.

Regards.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi harshitshah

one can try to debug how speed is selected in fec driver:

pay attention to line 1039:

/* 1G, 100M or 10M */

if (ndev->phydev) {

if (ndev->phydev->speed == SPEED_1000)

for debugging may be useful below link:

https://www.emcraft.com/som/imx-8m/debugging-the-imx-8m-som-using-arm-ds-5

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

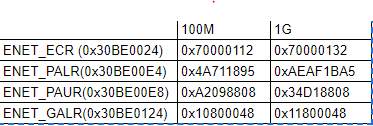

Thank you for your reply. I have gone through the code and checked for the configuration register map for the ENET Section for 1G and 100M speeds.

- Please find attached the configuration register settings for 1G and 100M. It looks like the register settings for the configuration are proper for 1G, however still not able to get the 1G speed working. Do you think any changes required in the configuration from the attached settings?

- We have probed the hardware and checked that there are signals on lines but we are not receiving anything from the software front. Do you think this is a hardware issue? We have submitted the schematics, signal net-length report in the main email chain.

Regards.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi harshitshah

regarding configuration register settings - you can test with i.MX8MQ EVK conected to

PC computer and dump register values, then compare them with custom case.

How did you know speed, had you used mii tool or smth else. below may be useful:

https://serverfault.com/questions/444382/changing-network-speed-to-1000mb-s

https://serverfault.com/questions/207474/how-do-i-verify-the-speed-of-my-nic

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi harshitshah

>have tried using the below command to check the speed.

># cat /sys/class/net/eth0/speed

>1000

seems you already have 1G speed.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

Yes, the speed is 1G, but the ping between both the processors is not working. (Please note that 100M is working fine in MAC<->MAC communication (using phy-less driver))

I am using following node of the device tree.

/* DTSI node */

fec1: ethernet@30be0000 {

compatible = "fsl,imx8mq-fec", "fsl,imx6sx-fec";

reg = <0x30be0000 0x10000>;

interrupts = <GIC_SPI 118 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 119 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 120 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clk IMX8MQ_CLK_ENET1_ROOT>,

<&clk IMX8MQ_CLK_ENET1_ROOT>,

<&clk IMX8MQ_CLK_ENET_TIMER>,

<&clk IMX8MQ_CLK_ENET_REF>,

<&clk IMX8MQ_CLK_ENET_PHY_REF>;

clock-names = "ipg", "ahb", "ptp",

"enet_clk_ref", "enet_out";

fsl,num-tx-queues = <3>;

fsl,num-rx-queues = <3>;

nvmem-cells = <&fec_mac_address>;

nvmem-cell-names = "mac-address";

nvmem_macaddr_swap;

stop-mode = <&iomuxc_gpr 0x10 3>;

fsl,wakeup_irq = <2>;

status = "disabled";

};

/* pin configurations */

pinctrl_fec1: fec1grp {

fsl,pins = <

MX8MQ_IOMUXC_ENET_TD3_ENET1_RGMII_TD3 0x1f

MX8MQ_IOMUXC_ENET_TD2_ENET1_RGMII_TD2 0x1f

MX8MQ_IOMUXC_ENET_TD1_ENET1_RGMII_TD1 0x1f

MX8MQ_IOMUXC_ENET_TD0_ENET1_RGMII_TD0 0x1f

MX8MQ_IOMUXC_ENET_RD3_ENET1_RGMII_RD3 0x91

MX8MQ_IOMUXC_ENET_RD2_ENET1_RGMII_RD2 0x91

MX8MQ_IOMUXC_ENET_RD1_ENET1_RGMII_RD1 0x91

MX8MQ_IOMUXC_ENET_RD0_ENET1_RGMII_RD0 0x91

MX8MQ_IOMUXC_ENET_TXC_ENET1_RGMII_TXC 0x1f

MX8MQ_IOMUXC_ENET_RXC_ENET1_RGMII_RXC 0x91

MX8MQ_IOMUXC_ENET_RX_CTL_ENET1_RGMII_RX_CTL 0x91

MX8MQ_IOMUXC_ENET_TX_CTL_ENET1_RGMII_TX_CTL 0x1f

>;

};

fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_fec1>;

phy-mode = "rgmii-id";

fsl,magic-packet;

status = "okay";

/* fixed-link node */

fixed-link {

speed = <1000>;

full-duplex;

};

};

1) Do you think we should change anything for the above device tree configuration? Please provide further debugging steps.

2) What should be the drive strength value in this case? Shall we update the same from the above values?

Regards.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi harshitshah

for ping issue suggest to post in kernel mail list, as this is general linux question