- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- RT1170 EVK FSL ROM API

RT1170 EVK FSL ROM API

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

RT1170 EVK FSL ROM API

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

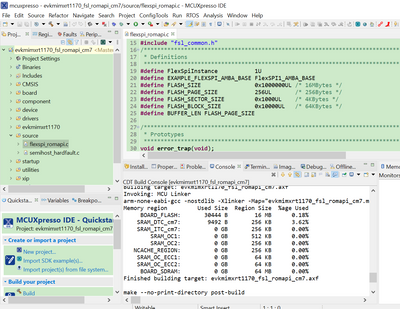

just looking at the RT1170 EVK FSL ROM API CM7 Example... MCUXpresso 11.4, SDK 2.10

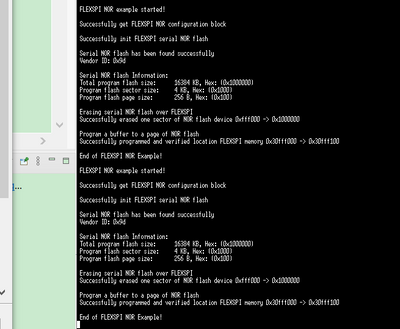

Built and debugged the project fine; it was able to successfully identify and erase/program the NOR Flash.

I'm creating a bootloader and am looking at this as the starting point; I was hoping to execute out of ITCM, to ensure that there are no issues accessing NOR (XIP) while it is being programmed.

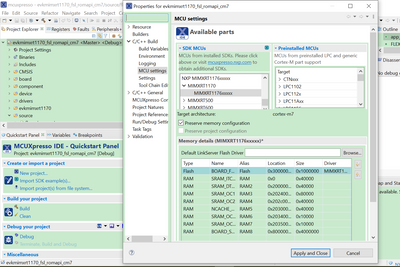

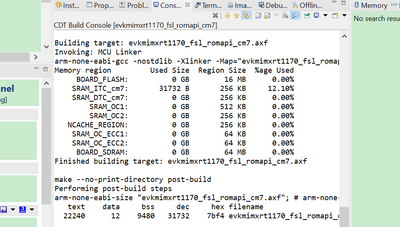

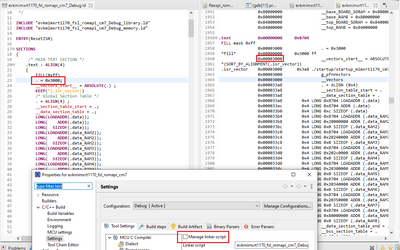

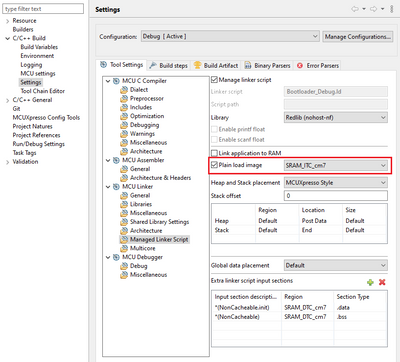

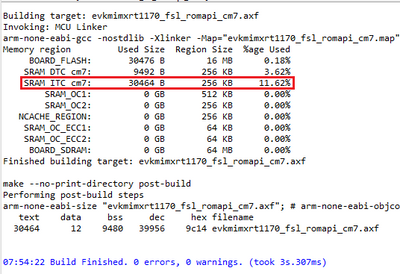

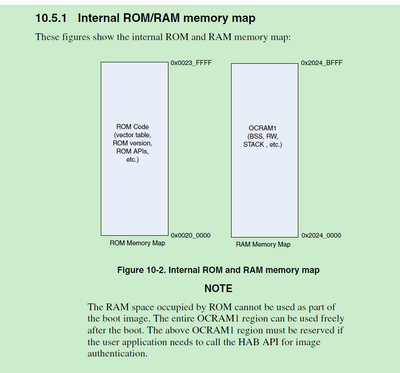

I made a couple minor changes to the project: in the linker options I specified "Plain load image" with SRAM_ITC_cm7; I removed OCRAM1 region from memory configuration since it overlaps with the ROM memory.

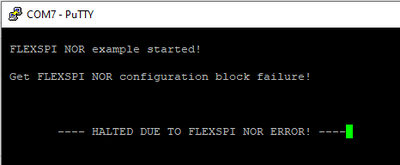

After this change, I can build and debug the project, and code is placed in ITCM correctly; however, the ROM_FLEXSPI_NorFlash_x() functions now fail with kStatus_InvalidArgument.

Unfortunately I can't step through the ROM code to figure out what's wrong...

Thought that it might be something to do with the FLEXSPI clock (serial_nor_config_option_t max_freq), but was wondering if anyone knew off the top of their head?

My assumption is that since the code was loaded from NOR to SRAM by ROM the FLEXSPI is set up correctly, but maybe detecting that the load/exec addresses aren't the same is bypassing this?

Thanks for the help,

Matt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mjosborne1

Thanks for your information, I know why you meet issues now.

As your used item: plain load image, it is not for RT, it is for the LPC series.

Please check the IDE install path document:

C:\nxp\MCUXpressoIDE_11.4.0_6157_prc1\MCUXpresso_IDE_User_Guide.pdf

page 189, chpater 17.8.4 Plain Load Image.

You will find it is desiged for the LPC540XX series, not for RT.

RT 1170 and LPC are totally different.

Now, if you want to run the code in the ITCM, please follow me, it will be success, and I have tested it on my side.

Now, if you want to run this ITCM code and boot from flash, you just need to generate the .s19 file, then use the MCUbootUtility tool to download to the external flash.

https://github.com/JayHeng/NXP-MCUBootUtility/archive/refs/tags/v3.3.1.zip

the related user manual is:

https://github.com/JayHeng/NXP-MCUBootUtility

Please note, RT series is the cross-over MCU, so the boot is different.

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kerryzhou, thanks for the info.

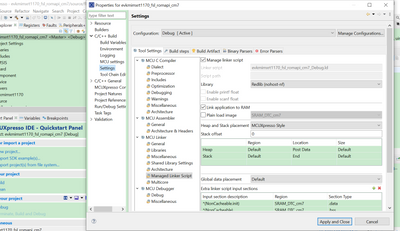

I was able to get the example running from ITCM when using the "Link application to RAM" option instead of the "Plain load image" option.

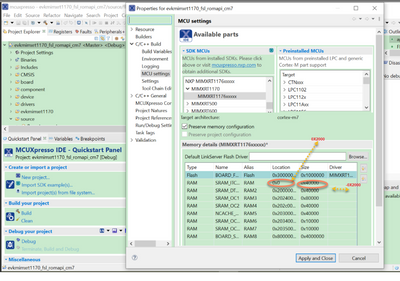

I do have the part set correctly for the i.mx rt1170 dev (MIMXRT1176xxxxx in the MCUXpresso MCU Settings), and the "Plain load image" option is always available for me even though I'm not using an LPCx.

So I just need to generate the boot headers for the RAM image at this point; I downloaded the MCU Boot Utility you linked and followed along with the user manual.

I set XIP_BOOT_HEADER_ENABLE = 0, even though "Link application to RAM" is specified and there is no boot header in the image.

I deselected "Manage linker script" and added the following vector table offset as suggested:

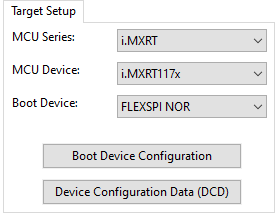

I configured the target as follows:

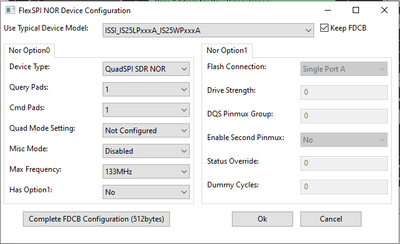

Boot Device Configuration:

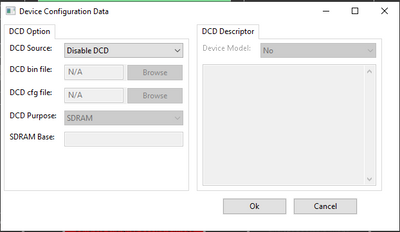

DCD Configuration (none, just using internal SRAM):

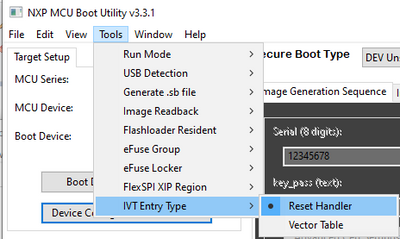

I also set the IVT Entry Type:

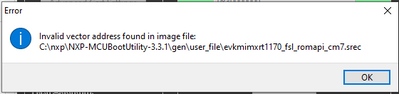

I connected to the EVK and selected the MCUXpresso output file; when I select "Generate Unsigned Bootable Image" I get the following error:

I tried to change the Tools -> IVT Entry Type to be "Reset Handler" and "Vector Table" but the result is the same.

In all cases I tried the resulting srec does not have any boot headers added.

Can you please try to reproduce this problem or point me to a procedure for this part/IDE/project?

I'm now trying to just add the initial XIP project boot headers manually to the RAM linked image; changing the entry point and boot data, but haven't had any luck yet...

Just to confirm:

- IVT "entry" value is the ResetHandler address in ITCM (0x0000_24E9)

- Boot data "start" value is the address of the start of ITCM (0x0000_0000)

- Boot data "length" value is the length of ITCM (0x0004_0000)

- RAM application is linked in ITCM at offset 0x0000_2000

- I chose 0x2000 instead of 0x3000 as the offset.

- Why is this offset needed?

- My guess is that ROM copies the entire image from NOR into ITCM, including the boot headers, and the execute address would be wrong without it?

- Is there a way to eliminate this offset using the IVT/boot params (maybe IVT "self")?

- Why is this offset needed?

- I chose 0x2000 instead of 0x3000 as the offset.

I've attached this binary image; it looks ok to me but won't boot.

Thanks again for the help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mjosborne1

If you want to run the code in the internal RAM, you don't need to generate the FCB, as the tool blhost in MCUbootUtility will help you to burn the FCB to the flash. Your provided RAM image don't need the FCB directly, FCB is used to configure the flexSPI interface to connect the external flash.

So, when you generate the code, you can use:

set XIP_BOOT_HEADER_ENABLE = 0, "Link application to RAM" is specified and there is no boot header in the image. This is correct.

Then when you want to use the MCUBootUtility tool to download the code, you can use your RAM none FCB code directly, I suggest you use the .s19, as that always contains the address information.

You can try none FCB RAM app attach to the MCUBootUtility tool download it again, that code will download to the external flash, and add the FCB automatically, then copy to the internal RAM to run it.

If you still have issues, just kindly let me know.

Don't check "Plain load image" option.

Wish it helps you!

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kerryzhou, thanks for the reply.

Yes, I understand that the RAM image built when specifying "Link Application to RAM" does not include any boot headers (FCB, IVT, Boot data) or the DCD; and that FCB is used to configure the FlexSPI interface.

I am still not able to get this to work using the MCU Boot Utility; I generated an S19 (I was using the .axf when using the "Image Generation Sequence" tab) and I still get the same error. I also tried the "Boot Device Memory" tab with the S19, and this also didn't work.

Were you able to use MCU Boot Utility to add headers and Flash the image that was linked to run from ITCM?

Can you please provide steps to do this?

Can you also please confirm the behaviour of the ROM bootloader with respect to the offset (i.e. the RAM app needs to be linked so that the execute address matches the load address offset in NOR)?

Thank you,

Matt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mjosborne1 ,

Please try the MCUbootUtility attached ITCM code, it is in this folder:

NXP-MCUBootUtility-3.3.1\apps\NXP_MIMXRT1170-EVK_Rev.A\cm7led_blinky_0x0000a000.srec

You can download this ITCM code to the flash, and test your board, whether the LED is blinking or not? If it is blinking, seems your side image still have issues.

Now, do you want to use the fsl rom code and run it in the internal RAM, and boot from external flash, right?

SDK_2_10_0_MIMXRT1170-EVK\boards\evkmimxrt1170\driver_examples\fsl_romapi\cm7

Please help to test cm7led_blinky_0x0000a000.srec on your side at first, if that works on your side, just the fsl_romap can't work please tell me, I will help to test it.

Please also note, you need to modify the memory offset to at least 0x2000.

Then try it again, if still have issues, let me know.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kerryzhou, thanks for the reply.

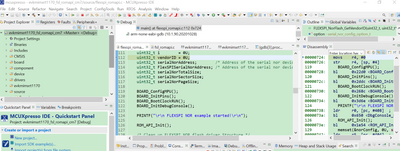

Yes, you should be able to reproduce using the EVK & SDK demo with just the following change:

When using this configuration, ROM_FLEXSPI_NorFlash_GetConfig() fails:

Thanks for checking this out!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mjosborne1

The original SDK ROM API mainly use the flash and DTCM.

What's your ROM_FLEXSPI_NorFlash_x is, do you mean x is related read, erase, etc?

In fact, you also can use the OCRAM, just don't use the ROM related OCRAM.

About your modified code, do you still use the flexspi_romapi.c, just modify the linker?

Please tell me the detail reproduction steps, then I can help you to check it.

Best Regards,

kerry