- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- PINMUX generation using NXP tool

PINMUX generation using NXP tool

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PINMUX generation using NXP tool

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are building a custom board using the Imx8mp processor.

I was going through the device tree thats present in the source and came across the pin mux configuration in the dts and the dtsi files.

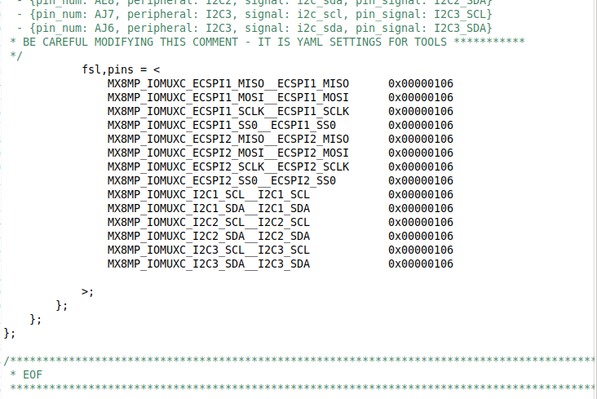

Example snippet from dts:

After going through the datasheets and reference manuals and some digging on the internet i came across the NXP provided pin config tool which generates the PIN mux config also.

But when I select these pins (for ex ECSPI2) the Pinmux tool generates completely different addresses.

And weirdly its generating the same address (106) nomatter what peripheral I add. (Snippet below)

So in actuality how do I get these addresses of these pins?

How do i proceed further to add our own peripherals to the custom board??

How can i add these adresses as a part of the device tree and get the board working?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello everyone,

i am starting to work on an evb toradex for imx95. in Particular i am starting to see the flexcan2 setting.

Looking in the macro “IMX95_PAD_GPIO_IO25__CAN2_TX” set in the file “imx95-pinfunc.h” I find :

#define IMX95_PAD_GPIO_IO25__CAN2_TX 0x0074 0x0278 0x0000 0x02 0x00

If I understand correctly, the structure of these macros is as follows:

<mux_reg conf_reg input_reg mux_val input_val>

0x74 is the mux_reg (offset of mux register)

0x02 is the value of mux_reg

0x278 i is the config_reg, and the related value is in dts file in iomux section

but I am not clear what they are and where to find the input_reg and input_val.

Can anyone give me some suggestions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

If you want to know the address you may refer to this file:

https://github.com/nxp-imx/linux-imx/blob/lf-6.1.y/arch/arm64/boot/dts/freescale/imx8mp-pinfunc.h

This macros definitions have the address for the Muxing of the pads.

You may use this file and the reference manual for correct Muxing and pad configuration for your custom board.

Saludos,

Aldo.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Even After going through the file I've not exactly understood how to get the adresses, as I'm looking at one of the dts files which uses the imx8mp (i.e the humming board pulse from solidrun), say ecspi2 node

Why do all the SCLK, MOSI, MISO have same adresses

Why do the adresses of the above 3 and CS look different?

Also, say i want to reconfigure one of the SAI pins as a GPIO and add the node in my dts, how can i get the adresses? How can i do it? Or more simply put how can i take any pin from the processor configure it as either an LED or a pushbutton?

Please provide us an elaborate answer as we are facing trouble regarding the same and we don't have much support...Thanks in advance!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please note that you're confusing the macro wich have the register address for the actual mux, and the configuration of such pin.

Each entry consists of 6 integers and represents the mux and config setting for one pin. The first 5 integers <mux_reg conf_reg input_reg mux_val input_val> are specified using a PIN_FUNC_ID macro, which can be found in <arch/arm64/boot/dts/freescale/imx8mp-pinfunc.h>.

The last integer CONFIG is the pad setting value like pull-up on this pin. Please refer to i.MX8M Plus Reference Manual for detailed CONFIG settings.

Example:

pinctrl_uart2: uart2grp {

fsl,pins =

<0x228 0x488 0x5F0 0x0 0x6 0x49>,

<0x228 0x488 0x000 0x0 0x0 0x49>;

};

Hope this helps,

Best regards/Saludos,

Aldo.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you so much for the elaborate reply.

That answered most of my questions.

But after going through the reference manual also, i was unable to find any information related the last integer CONFIG pad setting value.

Is there any standard values for set peripherals or it is listed in some document?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Glad to hear that it helped, for the CONFIG value you may refer to the reference manual, chapter 8.2.4 IOMUXC Memory Map/Register Definition.

In this chapter you'll find three types of register

SW MUX Control

SW PAD Control

Daisy

For the CONFIG you may check the SW PAD Control for each pad, note that it is almost the same for all pads, but please double check the values you want to have are correct.

Best regards/Saludos,

Aldo.