- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Clarification on TZ WDOG

Clarification on TZ WDOG

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Clarification on TZ WDOG

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Clarification/ Understand of TZ WDOG.

I’m designing a custom i.MX6UL design – From what I understand there are 3 external Watchdog signals (WDOG1-3_B which are either inputs or outputs). The Security Ref. Manual states that “TZ WDOG is another instantiation of the system WDOG.” (which is WDOG2).

QUESTION 1: Does this mean there are only 2 Internal Watchdog Timers but they could be mapped to either of the 3 external watchdog signals?

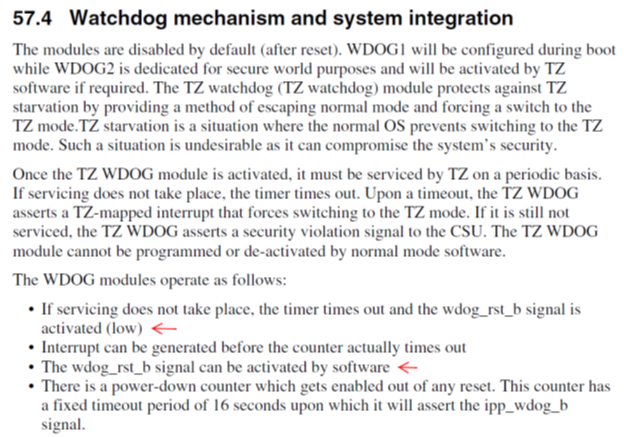

The following shows the operational states from Security Ref. Manual (Section 1.3)

If not serviced, the TZ WDOG security violation alarm goes to the SNVS.

Not certain if these States match the wording from the standard Reference Manual regarding TZ Wdog as follows:

The first Red Arrow indicates that wdog_rst_b is "Activated" but the second arrow indicates that it is Activated by software.

Question 2-4: Please clarify how wdog_rst_b is Activated (is software involved?)?

Can TZ Wdog only be mapped to external WDOG2_b?

Am I guaranteed that Reset (both internal and external reset) will happen due to TZ WDOG expiration and that it cannot be circumvented?

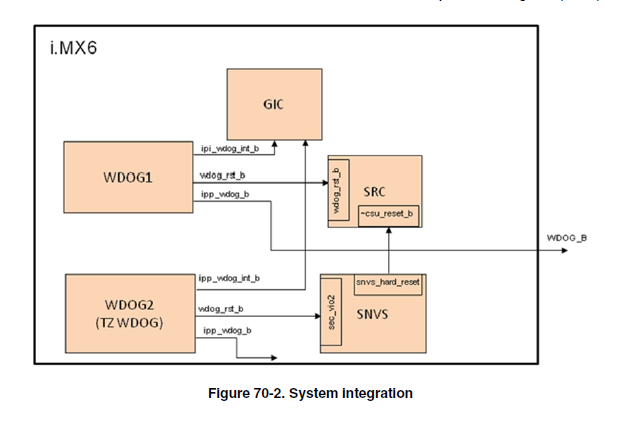

I found this diagram under Post 653405, but I don’t see anything similar under i.MX6UL.

Question 5: Is this a valid dwg. for the i.MX6UL?

Thanks

John Bacz...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please look at my comments below.

1.

IMX 6UL supports three watchdog timers (WDOG1/2/3).

Table 57-1 (WDOG External Signals) of i.MX 6UltraLite Reference Manual (RM),

Rev. 1, 04/2016, shows three separate sets of watchdog signals. Because of

pin multiplexing it is possible to select different pins for each of the three

watchdogs. But, say, TZ WDOG cab be mapped only to its external WDOG2 pin.

2.

Watchdog (time-out) events may be causes both either (hardware) timer one

or software, clearing bit SRS (Software Reset Signal) in WDOGx_WCR register.

3.

Use section 57.6 (Initialization) of the RM how to use the WDOGs.

4.

Register SRC Control Register (SRC_SCR) may be used to mask WDOG1/3 core resets,

but the TZ WDOG(2) cannot be masked. Also, the TZ WDOG module cannot be programmed

or deactivated by a normal mode SW.

Let me remind the Watch Dog Timer supports two comparison points

during each counting period. Each of the comparison points is configurable to evoke

an interrupt to the ARM core, and a second point evokes an external event on

the WDOG line.

5.

The figure, showing i.MX6 WDOG is applied to i.MX 6UL in general, take into account

three WDOGs of i.MX 6UL.

Have a great day,

Yuri

------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer

button. Thank you!