- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Inquiry about ls1024A CS2 and NAND CS.

ECC occurs when CS2 and NAND CS are used together.

ECC doesn't happen on NAND unless CS2 is used.

On page 56 of the datasheet, NAND_RE and NAND_WE are toggled when there is an access to CS#0-3.

There is a phrase like this, but it is judged that CS2 affects NAND RE/WE, so NAND CS also affects it.

What can I do to solve this problem?

I definitely need to use CS2.

Your help is much needed.

Thank you for the reply.

There is one thing I realized during the exam.

If CS2 is not used, ECC does not occur in NAND.

I am currently using CS2 with 20ms intervals.

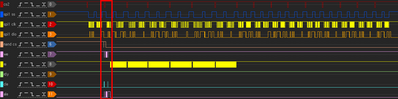

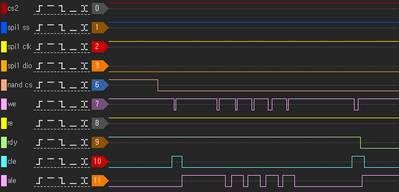

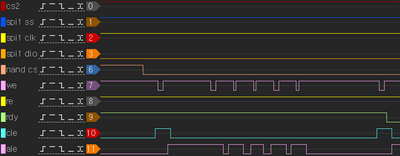

Please refer to the picture below.

Enlarging photo (above)

It can be confirmed that NAND_CS_n is active low and then changed to high.

With CS2, this situation arises.

I would like to know what part I need to pay attention to to solve this.

Thank you for answer

There's something wrong about what you saw

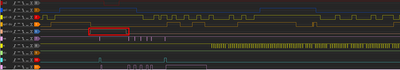

Please take a good look at the last photo I replied to

It can be confirmed that NAND CS is low active and high.

I don't know why the trigger got stuck, but I sensed something strange about this part.

It is judged that nand_cs is freed and proceeded again.

You need to check this part.

The part recognized by nand_cs is compared and passed.

It seems that the problem is not easily solved, but I think it will be solved if you help.

1. ECC Error (NAND_CS bad signal)

When NAND_CS is initially in a low active state, RE must be low active.

By the way, the re signal comes out as active, but I think that an error occurs in the data reading the nand flash because NAND_CS has become High.

2. NAND_CS signal ok

NAND_CS is operating normally.

Thank you for answering.

If NAND_CS and CS2 should not be Low Active at the same time, ECC should be continuously output when CS2 operates.

However, the ECC symptoms appear only when pasting files.

I think the cause is that the NAND_WE signal was not read early when NAND_CS went from LOW Active to HIGH.

But that doesn't mean you're wrong.

There is one thing I'd like to ask you.

Is there any way to unpack NAND_CS when reading CS2?

I think you should check when to operate CS2 and disable NAND_CS.

If you tell me how, I'll check that out.

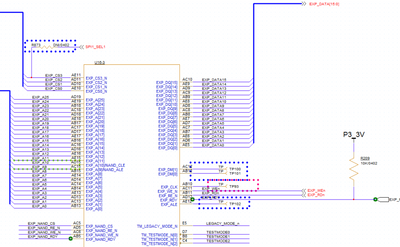

Thank you for contacting NXP support!

In theory, you don't have o experiment with any problem if you have a proper connection.

I attached for you an image of the proper connection of generic peripheral devices to LS1024A.

The pins NAND_RE and NAND_WE are independent of CS[0-3] and when you assert cs2 those pins don't affect the NAND function because NAND_CS_N (GPIO28) is not asserted.

The signals NAND_RE and NAND_WE always can be toggled because each signal indicates if the memory will be reeded o written and never should be asserted together

Please check your connections or share your schematic to check if exist a wrong connection.

Thank you for answer.

The circuit is like LS1024ARDB.

LS1024ARDB used NAND Flash same.(MT29F16G08CBACAWP )

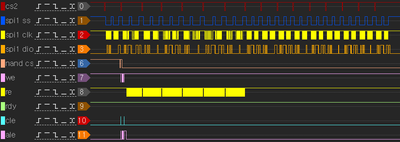

As a result of measurement with a logic analyzer, it was confirmed that CS2 and NAND_CS do not operate normally.

If CS2 is not used, NAND_CS operates normally.

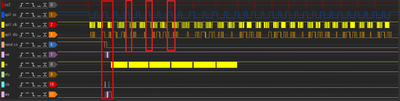

1. Use CS2, use NAND_CS_n => Logic analyzer measurement

NAND_CS_n photo enlargement

There are cases in which NAND_CS_n recognizes it as high at the point where it should become low active and then recognizes it as low again.

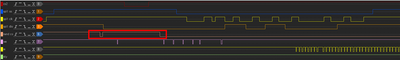

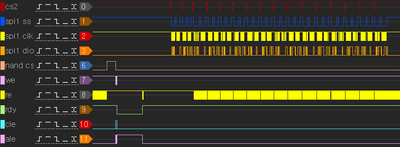

2. CS2 not used, NAND_CS_n used => Logic analyzer measurement

NAND_CS_n photo enlargement