- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- ソフトウェア・フォーラム

- :

- プロセッサ・エキスパート・ソフトウェア

- :

- Init_FB FB_TA_b pin not setup

Init_FB FB_TA_b pin not setup

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Init_FB FB_TA_b pin not setup

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have created a project in KDS3.0 + KSDK 1.2 and added the Init_FB component. I have setup all the options as they should be including defining the TA pin but the generated code never initialises the pin multiplexer.

In Driver Suite 10.4 + KSDK 1.1 the pin was setup in Common_Init() along with many others that were already configured in configure_fb_pins(). In KDS 3.0 + KSDK 1.2 the duplicates have been removed from Common_Init along with the TA pin but the TA pin configuration has not been added to the init_fb_pins function.

If I manually add PORT_HAL_SetMuxMode(PORTC,19UL,kPortMuxAlt6); to init_fb_pins then my board works again.

I have also tried to disable the TA pin in Init_FB and configuring it in PinSettings but still not working.

The only problem with me adding it manually is it gets overwritten every time I generate the Processor Expert Code again.

I did look at using the new fsl_flexbus component but I couldn't work out how to setup multiple chip select lines as each configuration specifies 1 address space but it appears only one configuration is active?

Also Does Chip specify the chip select line?

Best regards,

Adrian.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have researched the fsl_flexbus a bit more and found I can enable more than one chip select by calling FLEXBUS_HAL_Configure( FB_BASE_PTR, &MYCONFIG2 ); etc. from my code. However the TA pin is still never setup. So I the old Init_FB is still more convenient as everything (except the TA pin) is setup automatically at bootup.

Also I have found that the "Base address mask" parameter in the fsl_flexbus is shifted to the left 16 bits before being written to the CSMR? register so that difference needs to be taken into account when moving from the old Init_FB. The old Init_FB shows the calculated block size as confirmation of the correct mask which is nice.

Unfortunately the help on the component just states the obvious, e.g. "Base address mask - Base address mask." which doesn't really help.

Could someone tell me how to modify the Init_FB component to add the extra pin configuration?

Best regards,

Adrian.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

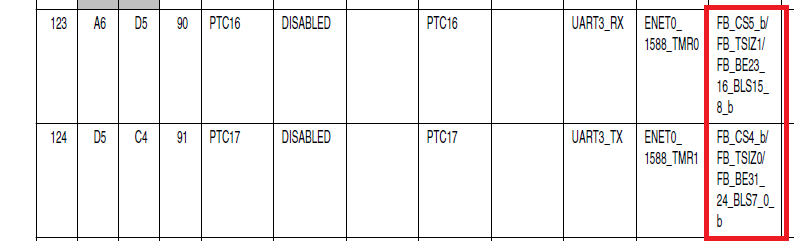

It appears that PORTC_16 and 17 have also got lost so I need to add:

/* Affects PORTC_PCR19 register */

PORT_HAL_SetMuxMode(PORTC,19UL,kPortMuxAlt6);

/* Affects PORTC_PCR17 register */

PORT_HAL_SetMuxMode(PORTC,17u,kPortMuxAlt5);

/* Affects PORTC_PCR16 register */

PORT_HAL_SetMuxMode(PORTC,16u,kPortMuxAlt5);

to the init_fb_pins function to get the flexbus to work with KDS 3.0/ KSDK 1.2

I have the Init_FB component's Chip select multiplexing - Signal CS4/TSIZ0/BE_32_24_select set to FB_BE_32_24 and Signal CS5/TSIZ1/BE_23_16 select set to FB_BE_23_16.

Best regards,

Adrian.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Adrian,

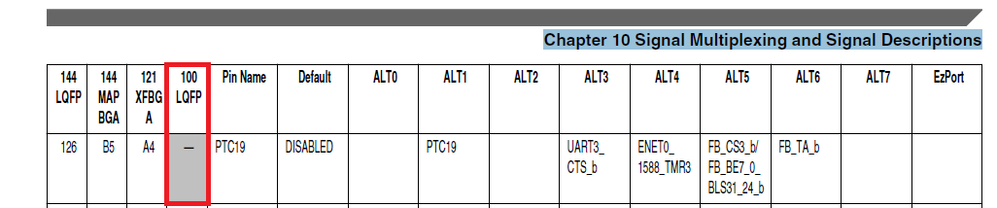

Which Kinetis derivative are you using in your application? Are you sure that you have selected the right package of the derivative? For example MK64FN1M0 derivative has several packages but the TA pin is not supported on MK64FN1M0VLL12 (100 pins package), see Chapter 10 Signal Multiplexing and Signal Descriptions in the reference manual:

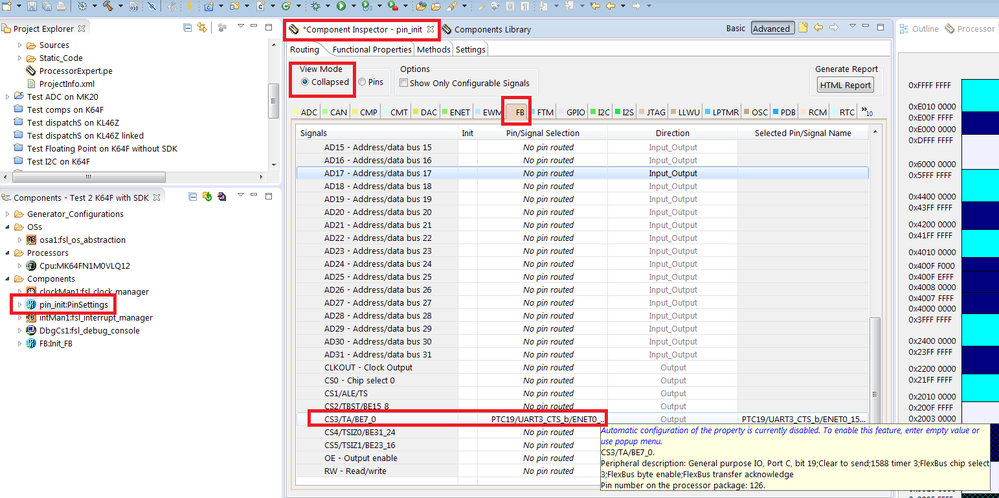

When you want to configure routing of pins you can also use the PinSettings component. In the Component Inspector of the PinSettings components select the Collapsed View Mode and the FB tab to configure routing of FB pins. See the following screenshot.

If these advices don't help you to resolve your issue send me the full name of the derivative (or the project) to reproduce the issue, please. I will send the issue to the responsible development team.

Best Regards,

Marek Neuzil

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Marek,

I have the MK64FN1M0VLQ12 package selected (144 pin package). All the pins appear on the PinSettings as expected.

I have tried to set the pins in the PinsSettings as well. For the FB_TA_b pin, if I select it in both the Init_FB component and the PinSettings, Pex generates an error but it doesn’t care about the other two pins. Either way the pins are not setup in pin_mux.c or anywhere else.

At the moment I have a file that has:

/* Affects PORTC_PCR19 register */

PORT_HAL_SetMuxMode(PORTC,19UL,kPortMuxAlt6);

/* Affects PORTC_PCR17 register */

PORT_HAL_SetMuxMode(PORTC,17u,kPortMuxAlt5);

/* Affects PORTC_PCR16 register */

PORT_HAL_SetMuxMode(PORTC,16u,kPortMuxAlt5);

and I keep this file open in KDS then copy / paste the contents to the end of init_fb_pins in pin_mux.c every time I generate the Pex code, which is a bit of a pain.

I have attached a project.

P.S. After cleaning the project in KDS I get the error ‘Program “make” not found in PATH’. This error was not there before but everything still builds as before.

Best regards,

Adrian.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Adrian,

I have checked the Init_FB on MK64FN1M0VLQ12 and I have reproduced the problem of the FB_TA pin routing. There are two alternative functions of this pin - FB_CS3_b/FB_BE7_0 and FB_TA that are selected by the MUX pins of the PORTC_PCR19 register but there is not support in the PinSettings for both alternate functions of this pin. I will report this issue to the Processor Expert development team.

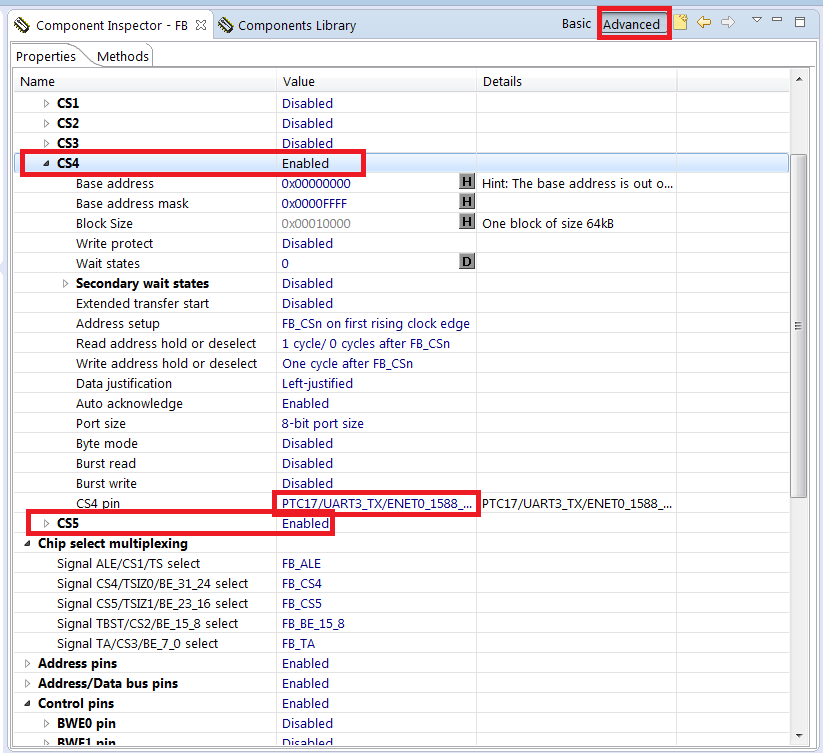

The CS4 and CS5 pins can be configured properly and the following code is generated in the init_fb_pins() funciton in the pin_mux.c program module:

void init_fb_pins(uint32_t instance)

{

. . .

/* Affects PORTC_PCR17 register */

PORT_HAL_SetMuxMode(PORTC,17UL,kPortMuxAlt5);

/* Affects PORTC_PCR16 register */

PORT_HAL_SetMuxMode(PORTC,16UL,kPortMuxAlt5);

/* Affects PORTB_PCR19 register */

PORT_HAL_SetMuxMode(PORTB,19UL,kPortMuxAlt5);

/* Affects PORTC_PCR11 register */

PORT_HAL_SetMuxMode(PORTC,11UL,kPortMuxAlt5);

}

I have configured (enabled) CS4 and CS5 pin functionality in the Chip Selects group of the Init_FB component, see below:

Best Regards,

Marek Neuzil

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Marek,

Thanks for looking at this. I think, with your help, I have the required settings for CS4/TSIZ0/BE32_24 and CS5/TSIZ1/BE23_16 now:

· Select FB_BE_32_25 and FB_BE_23_16 in the Chip select multiplexing section,

· Don’t select SIZ0 and SIZ1 pins in the Control pins section,

· Select the CS4/TSIZ0/BE32_24 and CS5/TSIZ1/BE23_16 pin settings in pin_mux:PinSettings component.

I feel like the BE32_24 and BE23_16 pins are missing from the Init_FB Control pins section (or the SIZ0 and SIZ1 pins should be multipurpose) as they are the only two that require me to delve into another component to configure.

(Edit: Note I'm not using CS4/TSIZ0/BE32_24 and CS5/TSIZ1/BE23_16 as chip select lines, they are serving the BE23_16 and BE32_64 functions.)

Just to be sure, when you report the TA pin problem to the Processor Expert dev team, to mention the TA pin setting in the Control pins section of the Init_FB component is not configuring the pin in pin_mux.c as I feel that is where it was meant to be configured.

Best regards,

Adrian.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Adrian,

The PTC16 and PTC17 pins cumulate the functionality of CS, TSIZ and BE. When you use these pins as BE (FB_BE23_16 and FB_BE31_24) the CS4, CS5, TSIZ0 and TSIZ1 functionality cannot be used (there are not any other pins that can be used), see the reference manual.

I have also received a workaround from the Processor Expert development team about the FB_TA pin routing. You can set the "Initialization/Call Init method" property to "no" and use the FB_TA pin pin routing code and the FB_Init() function in the main() function after PE_low_level_init() function call, see the following code:

int main(void)

/*lint -restore Enable MISRA rule (6.3) checking. */

{

/* Write your local variable definition here */

/*** Processor Expert internal initialization. DON'T REMOVE THIS CODE!!! ***/

PE_low_level_init();

/*** End of Processor Expert internal initialization. ***/

/* Affects PORTC_PCR19 register - TA pin */

PORT_HAL_SetMuxMode(PORTC,19UL,kPortMuxAlt6);

FB_Init();

. . .

Bes Regards,

Marek Neuzil

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Marek,

Thanks for the tip. I have now added the SetMuxMode line to main() as you suggested and that works. I have found that I can keep the auto initialise set and therefore don't need to call FB_Init so much easier now.

As far as the BE signals go, I realise that functionality is exclusive and I am just using the pins for that function. My observation was simply that to enable the pins as BE I have to use the pin_mux:PinSettings component as well as the FB_Init settings, whereas the other FlexBus pins are configured for me in the FB_Init component so it just seems inconsistent.

I very much appreciate your time and help.

Adrian.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Adrian,

The defect has been fixed and the fixed component will be available in the next release of Processor Expert for KSDK 1.3.0.

Best Regards,

Marek Neuzil