- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- PowerQUICC Processors

- :

- MPC8270 GPCM Burst Read/Write Timing

MPC8270 GPCM Burst Read/Write Timing

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC8270 GPCM Burst Read/Write Timing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The MPC8270 executes out of SRAM and the MPC8270 is configured to execute in GPCM mode. The MPC8270 is configured as an "Single MPC8270 bus mode" (with BCR[EBM] = 0). But the Extended transfer mode is enabled (BCR[ETM]=1). The datasheet says "Note the GPCM does not negate CS in back-to-back reads to the same device when in single MPC8280 bus mode or in 60x-compatible bus mode with extended transfers enabled."

THe data sheet also says "The GPCM provides interfacing for simpler, lower-performance memory resources and

memory-mapped devices. The GPCM has inherently lower performance because it does not support bursting."

But i do see that that burst reads/writes of 32 bytes (4 double word reads/writes on 64 bit port) are executed from time to time at least for cache reads/writes (maybe because of ETM).

The question is : Is there somewhere in the datasheet or a pdf which shows the timing diagram for the memory controller (GPCM) in this configuration (burst read/write)

I do see that the CS# remains asserted continously for 4 double word reads. I do see that the OE# or WE# gets asserted and deasserted for each of those double word reads within the 32 byte block.

I have the CSNT bit set to provide a quarter clock cycle delay between the WE# getting deasserted to the CS# being deasserted. How does this work during a burst read/write when CS# remains asserted for 4 double words? When does the data/address change wrt to WE# within a burst cycle?

I couldnt find this in the app note AN2176

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Normally GPCM does not support bursting, so "I do see that the CS# remains asserted continously for 4 double word reads" sounds unusual. Do you have a waveform? Better if it contains also PSDVAL and TA signals.

Regards,

Bulat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We were also surprised to see this.

Attached is the waveform..

Test is the chip select.

In “ain”, bit 0 is not included. So the address has to be left shifted by 1.

We couldn’t include PSDVAL in this. But PSDVAL is same as nTA

The four addresses are contiguous and on an 8 byte boundary.

Burst Read

Burst Write

Sai Krishnan Jagannathan

Technology Specialist

Honeywell | HPS GTS HW

Office: +91 80 26588360 x41342

sai.jagannathan@honeywell.com

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you also let me know values of BR and OR registers of the GPCM port shown in the waveforms?

You wrote "burst reads/writes ... are executed from time to time at least for cache reads/writes". Why did you decide that waveforms show cache read/writes?

Regards,

Bulat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

BR : 0x0000 0C01

OR: 0x0000 0812

The datasheet talks about a cache block being 32 bytes and requiring 4 beats of 8 byte write.

Also we see the nTA toggling once every 64 bit access within a burst.

We don’t find an instruction which is 64 bit. As in loads/stores only read/write 32 bit at the maximum.

So based on these, our guess was that the bursts are being initiated as part of cache reads/writes.

Maybe the DMA reads/writes through the cache.

Regards,

Sai

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

BR : 0x0000 0C01

This BR value means you are using 8-bit GPCM port with RMW parity. Is this correct?

Regards,

Bulat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The PS is set to 00 (64 bit)

And DECC is set to 11 (ECC)

I made a mistake in the BR value

It is 0x0000 0601

sai.jagannathan@honeywell.com

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, actually your waveforms are not unusual. This kind of timing is expected. When the Manual says "The GPCM ... does not support bursting", it means GPCM is not able to place data beats onto back-to-back clock cycles during a burst, like SDRAM machine or UPM. Note that we nowhere state that GPCM's CS is negated between data beats during a burst transaction.

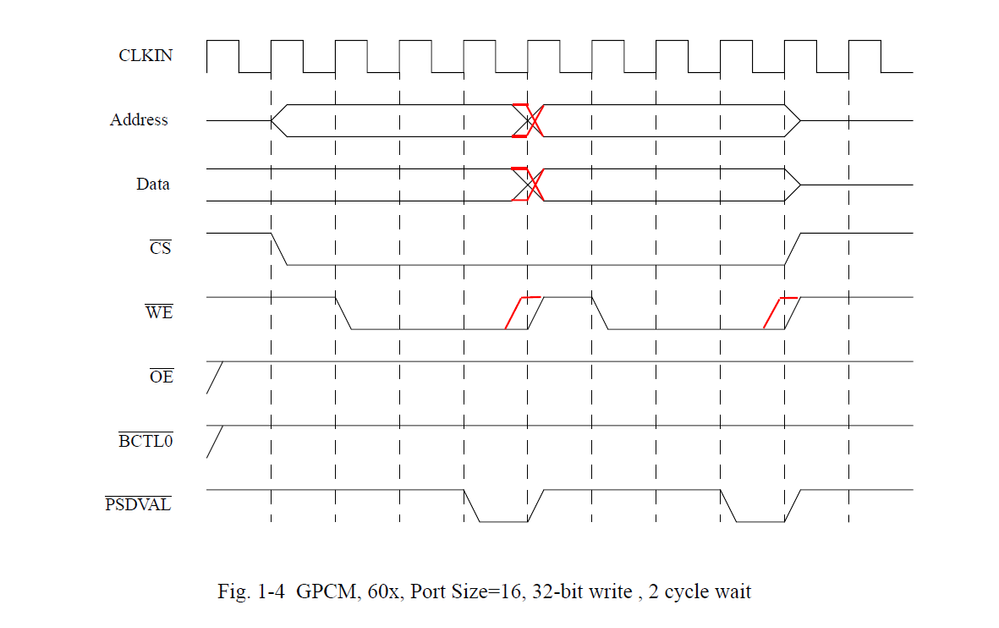

Answering your question " Is there somewhere in the datasheet or a pdf which shows the timing diagram for the memory controller (GPCM) in this configuration (burst read/write)", we do not have such diagrams in the documentation. However the Manual states following: "Although GPCM does not support bursting, the internal logic will split a burst into individual beats that the GPCM can support." So actually the GPCM's burst consists of back-to-back single beat cycles. Examples of back-to-back single beat cycles can be found in the AN2176, figure 1-3 shows two back-to-back reads, figure 1-4 shows back-to-back writes. Both are pretty similar to your waveforms with different number of wait cycles.

Regards,

Bulat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks.

The two figures seem to show the transactions for a 32 bit port.

We have a 64 bit port. I didn’t find any where that the CSn will remain deasserted for multiple 64 bit transactions (apart from the cache reads/writes). (which is what we are seeing)

Nevertheless, what I am really looking for in the timing diagram is how how WEn behaves when the CSNT bit is set. (CSNT bit from the ORx (options register of GPCM))

CSNT = 1 deasserts the WEn a quarter clock cycle before the CSn (deassertion) providing additional hold time.

But since the CSn remains LOW for multiple 64 bit transactions, what timing does the WEn follow.

Does the WEn get deasserted quarter clock cycle before the rising edge of CLK for every 64 bit transaction (or)

Does it do that only for the last transaction before the CSn gets deasserted?

Sai

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Normally there is no such a term as "... multiple 64 bit transactions (apart from the cache reads/writes)", only single-beat 64 bit (or 8-bit/16-bit/32-bit) transaction and 32-byte burst (that is four 64-bit beats). "Normally" means BCR[ETM]=0. If BCR[ETM]=1, then the CPM (not the core) is able to use also 16-byte and 24-byte transactions.

Your understanding of CSNT behavior is not correct. If CSNT=1, WEn is deasserted 1/4 clock cycle before Address/Data Invalid, not "a quarter clock cycle before the CSn (deassertion)". This in particular means that CS does not have to be deasserted during backto-back GPCM read/write cycles. Please see table 11-31 of the Ref Manaul for details. Figure 11-44 shows this case.

I have edited a figure 1-4 from the AN2176 to illustrate CSNT=1 case, see picture. If your logic analyzer had better resolution, you would see this kind of WE timing.

Regards,

Bulat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Bulat,

This is the confirmation I was looking for.

Thanks,

Sai

Sai Krishnan Jagannathan

Technology Specialist

Honeywell | HPS GTS HW

Office: +91 80 26588360 x41342

sai.jagannathan@honeywell.com