- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- Other NXP Products

- :

- MC50XS4200BEK SO Register reading is not working as per data sheet

MC50XS4200BEK SO Register reading is not working as per data sheet

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MC50XS4200BEK SO Register reading is not working as per data sheet

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are using MC50XS4200BEK for load driving. Reading of the register contents is not working as per data sheet. First we write SI STATR register which contains address of the SO register. Then generating 16 clock pulses by sending same word. During second cycle the expected word is the required SO register. But, actually getting the SI STATR register as we write it previously. The observation is whatever the register we write previously is shifting out in the next cycle, irrespective of SI STATR contents.

Thanks

Satheesh Kumar K

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Satheesh,

Do you have a logic analyzer or an oscilloscope to see what is going on the bus? Could you please post it here?

Best regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tomas,

Thank you for reply.

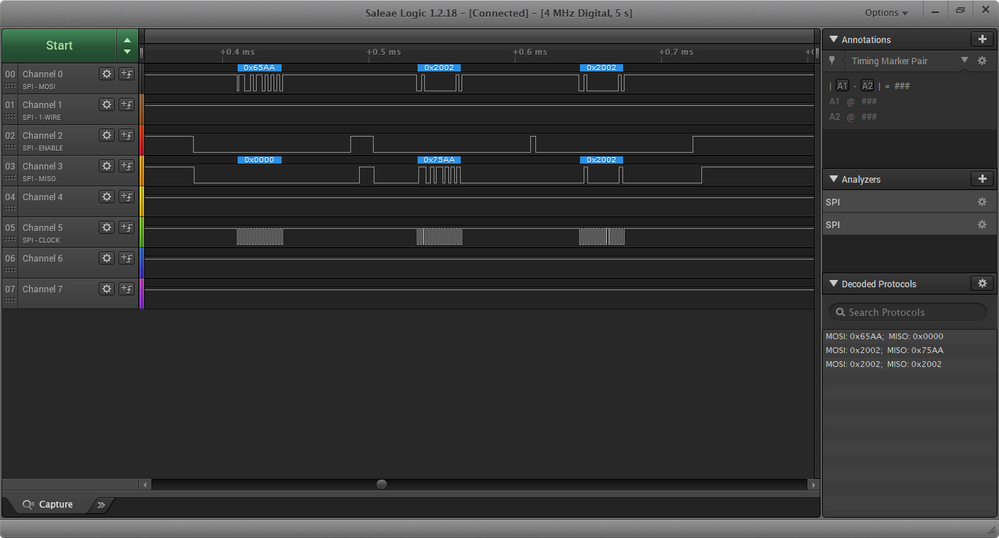

Here I attached screen shot of SPI bus data captured through logic analyzer.

Channel 0 - MOSI

Channel 1 - RSTB pin, which is always high

Channel 2 - CSB

Channel 3 - MISO

Channel 5 - SCLK

Thanks & Regards

Satheesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Satheesh,

From your waveforms, SCLK is idle high. Note that the MC50XS4200 is compatible with SPI Mode 1 which means that the SCLK signal should be idle low, data are read on the falling edge of clock signal and changed on the rising edge.

Also please make sure that the timing requirements, as shown in Table 5 and Figure 7 of the MC50XS4200 datasheet, are met.

I hope it helps.

Best regards,

Tomas