- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5746R SWT disable

MPC5746R SWT disable

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5746R SWT disable

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

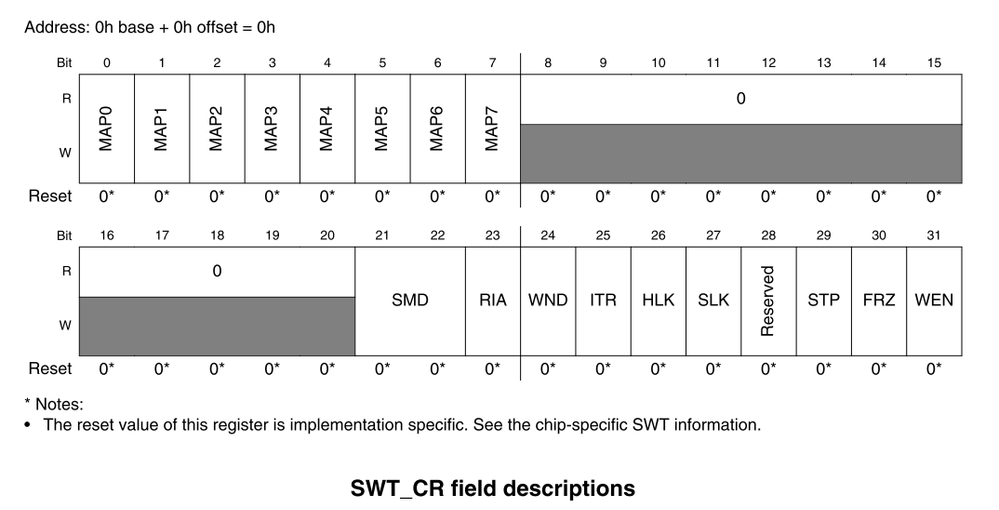

Hi, in the AN4670 document and also in the generated startup.S code in S32DS it states that to disable the SWT the SWT_CR field should be set to 0xFF00010A, but according to the ref. manual the "A" would write on a reserved bit. Is bit 28 reserved or not?

Also only SWT1 should be enabled by default but when looking at the memory on position 0xFC050000 (SWT0) it reads 0xFF00011B, why is that?

Another issue/question is that in the generated startup.S (from S32DS) there is code to disable the SWT1 also for core 0....

A bit off topic ... but...I noticed that the crt0_core1_flash.s in AN4670 does not init the registers in the same order as in the startup.S....which of the two is the preferred way of doing it?

Finally I also have a problem with IVOR1 when writing to the registers....does anyone have a working example on how/when to enable the SWT? (I have already looked at Example-MPC5744P-SWT-Short-reset-v1_1-GHS614 without any success....)

Thanks,

Cecilia

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This is quite simple. Just write in SWT WEN bit on watchdog you want to disable. You have to unlock CR register before write.

Always stick with RM and not with some S32DS examples. Reserved bit must be leaved untouched or it can lead to unpredictable behavior.

You can control from any core any SWT.

This Example-MPC5744P-SWT-Short-reset-v1_1-GHS614 is working correctly. Just have in mind that debugger by default disables SWT and you have to enable it in debugger if you want to debug this example!

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How does the debugger disable SWT, could it have anything to do with the bit 28 always being set to 1 at startup?

//Cecilia