- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MPC5634M eSCI- LIN mode.,Receiving message error

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi ,

I am learning the MPC5634M Microcontroller Reference Manual.

I have some questions about eSCI/LIN receive.

uint8_t LINFlex1MasterSendHeader(void)

{

uint16_t timeout,j;

uint8_t Ret=LINFLEX_E_OK;

uint32_t temp_data = 0;

FrameHeaData[0] = 0x36;

FrameHeaData[1] = 8;

FrameHeaData[2] =0xCF;

FrameHeaData[3] = 0xFF;

for (j=0; j< sizeof (FrameHeaData); j++)

{ /* Loop for character string */

while (ESCI_B.SR.B.TXRDY == 0)

{

timeout++;

if(timeout>LINFLEX_TIMEOUT_VAL)

{

Ret = LINFLEX_E_NOT_OK;

break;

}

else

{

/**/

}

} /* Wait for LIN transmit ready = 1 */

ESCI_B.SR.R = 0x00004000; /* Clear TXRDY flag */

ESCI_B.LTR.R = FrameHeaData[j]; /* Write byte to LIN Trans Reg. */

}

LINFlex1ReceSigh = 0;

return Ret;

}

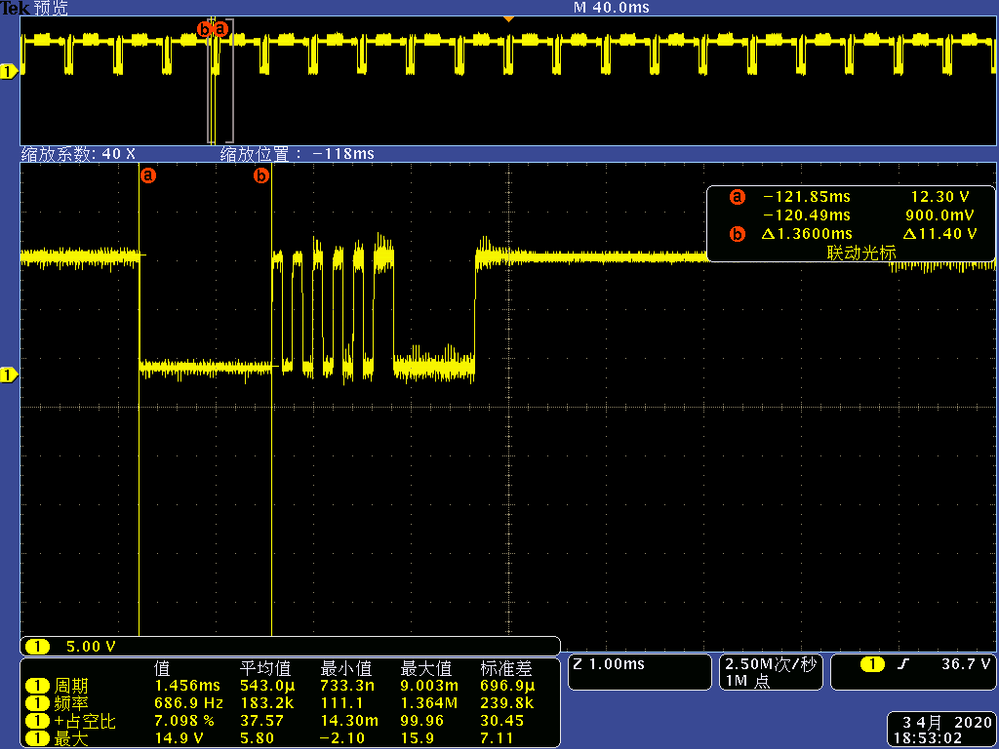

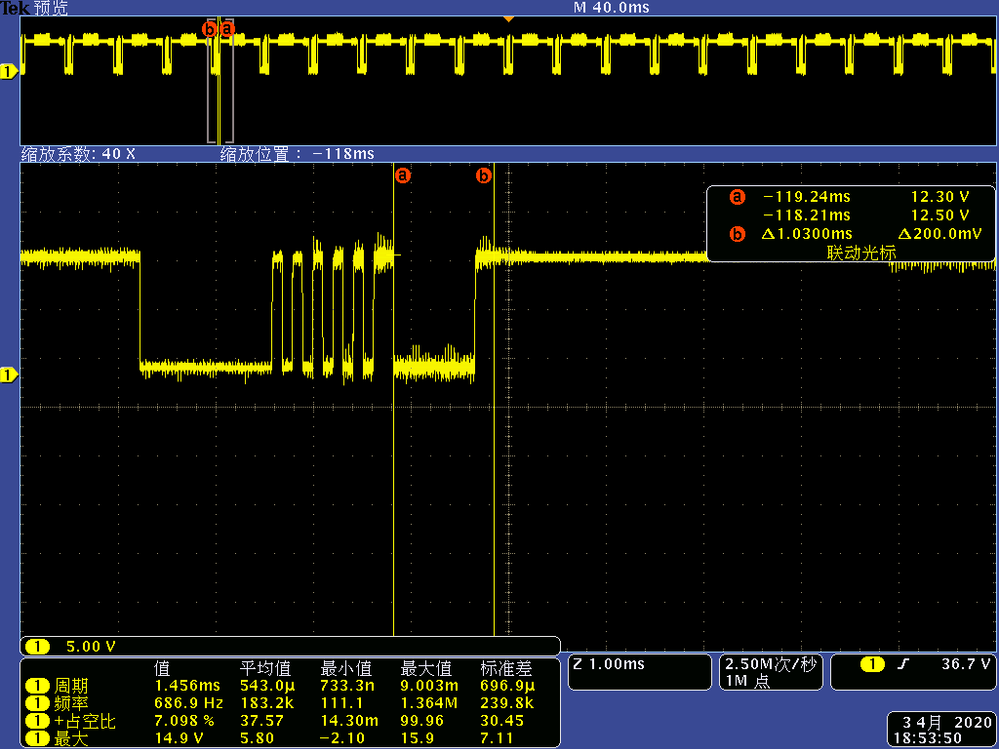

The resulting waveform is as follows

- LIN break field

- LIN synch field

LIN identifier field

- The identifier field is wrong from the waveform, so the received data is abnormal.,and the waveform remains consistent regardless of the ID

MPC5634M Microcontroller Reference Manual.

The first byte written to the SCI_LTR contains the Identifier and Identifier Parity fields. The second byte

written defines the number of data bytes requested from the LIN slave. The third write access defines the

CRC and checksum checking. The TD bit has to be set to 0 to invoke the RX frame generation. The TO

field defines the upper part of the timeout value. The fourth byte written defines the lower part of the

timeout value.

After the fourth byte is written the generation of a LIN RX frame starts. Firstly, a break field is transmitted,

then the synch field and the protected identifier field.

The actual operation is not as expected,So please help to analyze the causes of this problem. Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

how is the LTR defined? Do you really write a BYTE to address offset 0x10?

If LTR is defined as 32 bit register then use this statement

ESCI_B.LTR.R = FrameHeaData[j] << 24;

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Petr

Thank you for your answer.Your writing is correct.

Thanks