- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Is this an e200z6 embedded Floating-Point APU implementation issue?

Is this an e200z6 embedded Floating-Point APU implementation issue?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In section 3.6.4.1 "Options for Embedded Floating-Point APU Implementations" of the e200z6 PowerPC core manual, the following option implementation is stated:

Option: If an operand for a calculation or conversion is denormalized, the implementation may choose to use a same-signed zero value in place of the denormalized operand.

e200z6 Implementation: The e200z6 uses a same-signed zero value in place of the denormalized operand.

However, this appears to not be true.

For example, given the following two single-precision float variables with values as shown:

float a = 1.98e-43; //(0x0000008D)

float b = -125; //(0xC2FA0000)

Any equation or comparison between these two operands (ex. "a + b" or "a > b") results in an SPE Data Exception due to inexact result (FINXS and FINVS bits set in the SPEFSCR). Based on the implementation described in the manual above, I would have expected that the FPU would use the "same-signed zero value" in place of the denormalized value stored in variable 'a' and not throw an exception. Have I misunderstood the manual, or is this actually an issue in the floating-point APU of the e200z6 core?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, SPE allows two options single precision floating point capabilities:

1) May be configured to be fully IEEE compliant, in which case awkward corner cases (NaN’s, Infinities, denormalized values) will be handled by software through the raising of exceptions

2) May be configured to be not fully IEEE compliant, in which case arithmetic will saturate or round to zero and no value-dependent exceptions will be raised

Option number 2 is default, so yes, underflow value is replaced by 0 automatically by default.

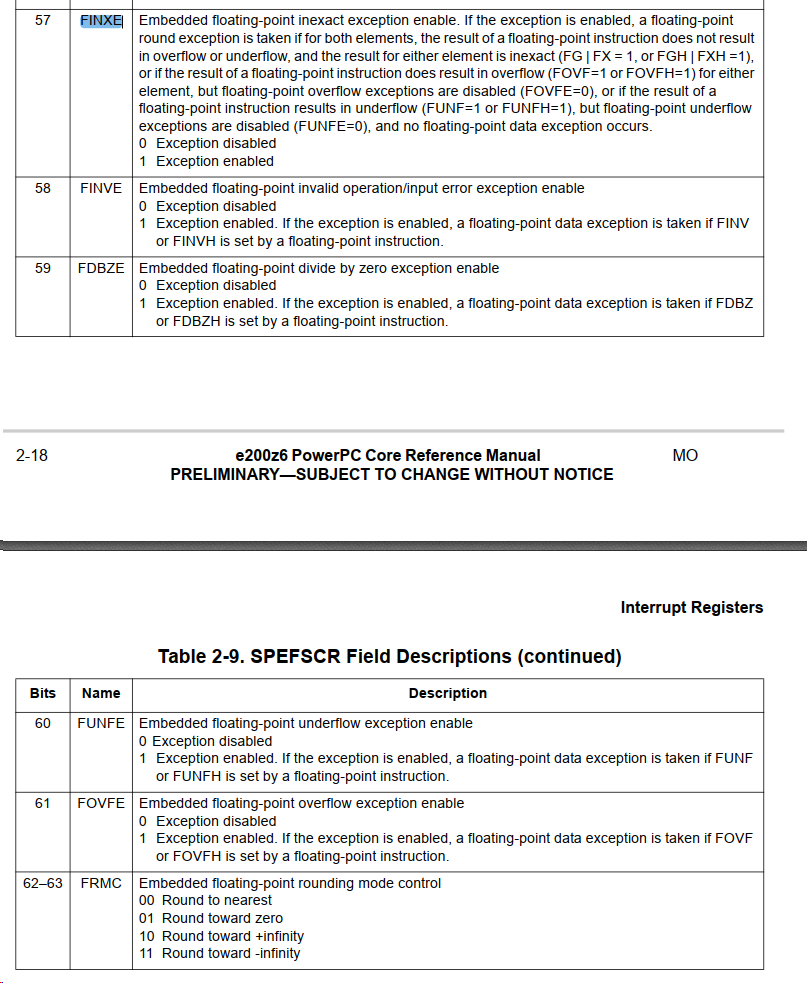

Pay attention to SPEFSCR bits below:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

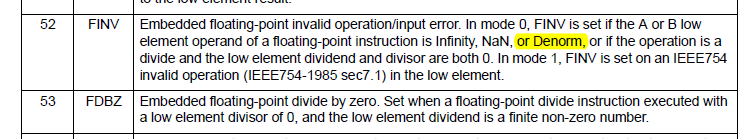

Thanks David. That answers it!. I do indeed have FINVE set so that's the reason for the exception.

I guess I missed this statement:

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, SPE allows two options single precision floating point capabilities:

1) May be configured to be fully IEEE compliant, in which case awkward corner cases (NaN’s, Infinities, denormalized values) will be handled by software through the raising of exceptions

2) May be configured to be not fully IEEE compliant, in which case arithmetic will saturate or round to zero and no value-dependent exceptions will be raised

Option number 2 is default, so yes, underflow value is replaced by 0 automatically by default.

Pay attention to SPEFSCR bits below: