- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

How to correctly configure CAN Rx Mailboxes Mask Register in MPC5748G?

I want to receive message with specific ID .For instance 0x000,0x111,0x222 and so on.

- The can configuration is as follows:

- The can_fifo_config is as follows:

- I send message to my device from ID 0X000 to ID 0X7FF,while the device receives something that is not in my expectation.

As follows:

It seems that the mask highest bit is not in effect.

0 - 400:

0000 0000 0000

0100 0000 0000

44 - 444:

0000 0100 0100

0100 0100 0100

111 - 511:

0001 0001 0001

0101 0001 0001

Because of the RX FIFO,it is right that to configure the CAN_RXFGMASK as 0x1fffffff. [0:28]

However there are some mistakes in somewhere.

Then I force CAN_RXFGMASK to be configured as 0x3fffffff. It does work.

Is there some mistakes in my knowledge?

where is mistake?Please inform me in detail .

regards.

已解决! 转到解答。

Hi,

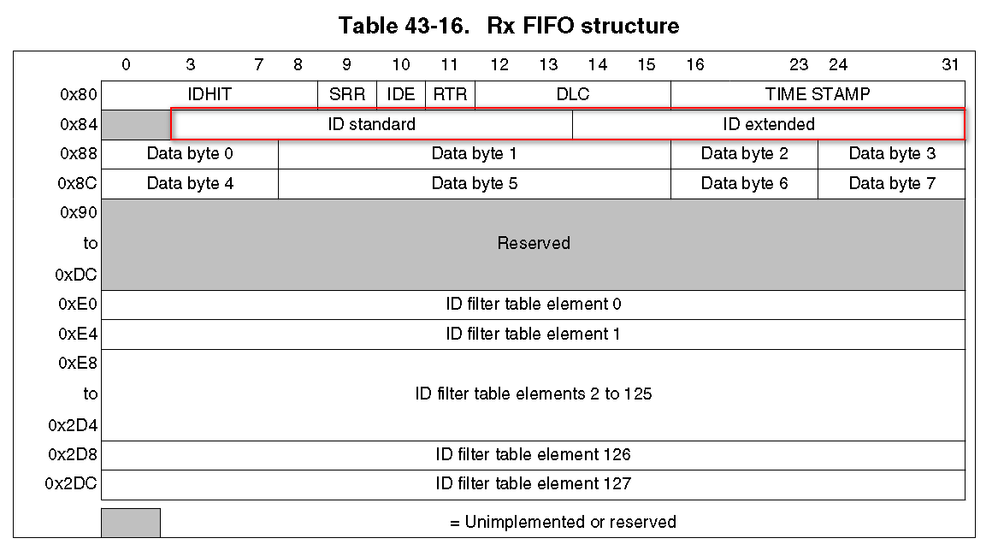

mask within a RXFGMASK should be shifted left by 1 bit as you can see in chapter 43.4.17 of the RM

so, to have exact match you need to set RXFGMASK = 0x3FF80000 (assuming standard ID is received).

Most probably the driver function does not shift the value properly.

With the RXFGMASK = 0x1FFC0000 the MSB of the ID is don't care, that's the reason you received such IDs.

BR, Petr

Hi,

mask within a RXFGMASK should be shifted left by 1 bit as you can see in chapter 43.4.17 of the RM

so, to have exact match you need to set RXFGMASK = 0x3FF80000 (assuming standard ID is received).

Most probably the driver function does not shift the value properly.

With the RXFGMASK = 0x1FFC0000 the MSB of the ID is don't care, that's the reason you received such IDs.

BR, Petr

Thank you for your reply.

Yes,you are right.

There may be a bug in the SDK.

The API(settting Rx FIFO global mask) dose not deal with CAN_MCR[IDAM] .

It only checks either standard id or extended id,but it is useless for CAN_RXFGMASK.

And it will clear the bits form 31 to 29. So it is never correct that use the API(FLEXCAN_DRV_SetRxFifoGlobalMask) to configure the CAN_RXFGMASK.

Best regards,gao

Hello, Mr. Gao,

@泽乾 高

Could you share the code you showed?

I just want to know how to use RxFIFO to receive CAN MSG with multiple CAN IDs. I am using the API(status_t FLEXCAN_DRV_ConfigRxMb) to receive CAN MSG now ,but it can only receive the msg which CAN ID was defined.

Many Thanks~

You can configure the mask as follows:

FLEXCAN_DRV_SetRxMbGlobalMask(instance, FLEXCAN_MSG_ID_STD, 0x0U);

(void)FLEXCAN_DRV_SetRxIndividualMask(instance, FLEXCAN_MSG_ID_STD, Individual_num, 0x0U);

Hope it works for you.

Regards.