- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Configuration of NMI line from SBC to MPC5777C for INTB?

Hi,

I am using FS6513CAE with MPC5777C in the project. The pin INTB is connected to the NMI pin of MCU. The INTB is generating an interrupt when IO_0 undergoes state change(Verified on oscilloscope). The SIU_EISR register doesn't show the NMI0 bit getting changed(Stays 0- No NMI event has occurred on the NMI input of Core0). So, MCU is not acknowledging the interrupt & ISR is not getting hit obviously. IVOR1 handler is present in the project.

Current configurations done on MCU for the NMI pin-

1. GPIO pad 213 configured as NMI alternate functionality, pin direction is input only.

2. SIU.DIRER.B.NMISEL8= 0; /*Routing interrupt as NMI (IVOR1 handler) to Core0*/

3. SIU.IFEER.B.IFEE_NMI8= 1; /*Enabling the falling edge event for Core0*/

Have I missed any part of the configuration; because of which, I am not getting interrupt acknowledged in the SIU_EISR register???

Thanks in advance.

The bits EE & ME in MSR(Machine state register) of the core(e200z759CRM) are also made 1 in order to enable the machine check exceptions.

Please respond!

Hi, I have just created example based on setting you have shared:

Example MPC5777C-SIUL_External_NMI GHS714

It is just working fine.

SIU.DIRER.B.NMISEL8 = 0 and SIU.IFEER.B.IFEE_NMI8= 1 is the all needed configuration.

MSR[ME] does not mask NMI, it may stay cleared.

Hi David,

1. As NMI is the user switch input in this example; why was NMI0 bit not cleared in place of EIF0 in Machine_check_handler()?

2. The description(comments in the code) says rising edge will be considered as detection of NMI, but IFEER register is configured in the code; is it because either of them is configurable here, as switch press & release would generate both?

3. Could u share the screenshot of the EISR register being set & waveform of the output being toggled(LED)?

4. I've rechecked the parameters, but still there is no NMI0 bit being set in EISR register.

Thanks in advance.

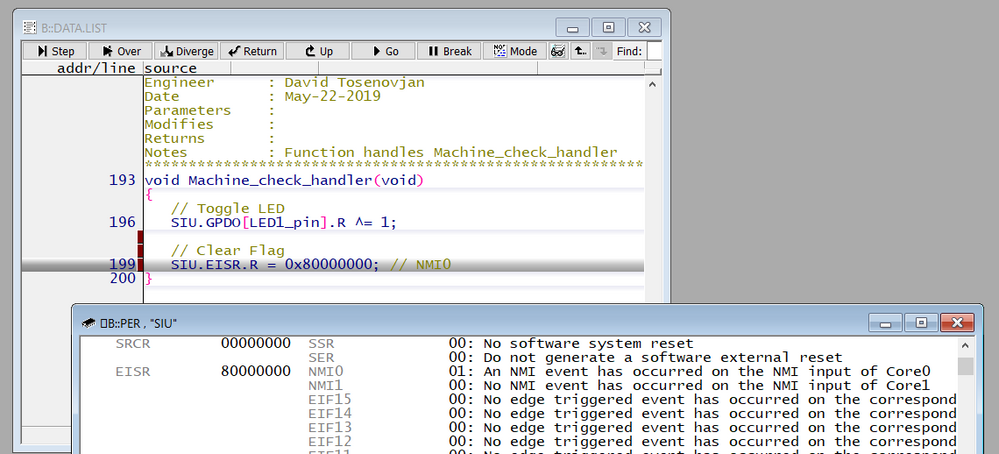

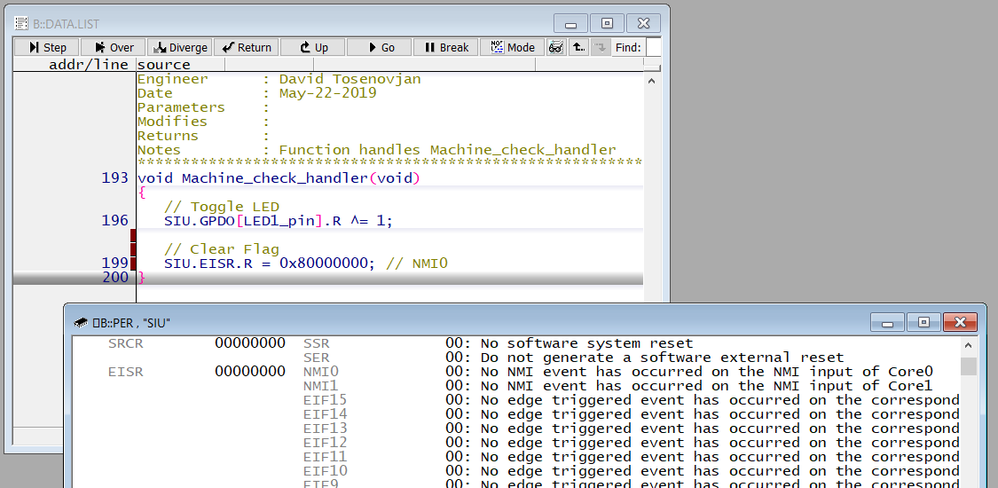

1) Yes, you are right. I have just corrected it.

void Machine_check_handler(void)

{

// Toggle LED

SIU.GPDO[LED1_pin].R ^= 1;

// Clear Flag

SIU.EISR.R = 0x80000000; // NMI0

}

It worked with SIU.EISR.B.EIF0 = 1 as well but only as coincidence of improper usage of .B instance. Pay attention to following document, section 3.2:

http://www.nxp.com/files/32bit/doc/eng_bulletin/EB758.pdf

2) Just a typo int the comment. But pressing of button may be configured for any of the edge, either it reacts of press or release.

3, 4)

4) Just to note example suspect jumper below, position 1-2 as OPEN.