- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- MCUXpresso SDK

- :

- Two continuous LPSPI blocking transfer

Two continuous LPSPI blocking transfer

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Two continuous LPSPI blocking transfer

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have to read data from a serial Nor flash, connected to my RT1xxx through LPSPIx.

I have to send one command byte and then I have to read 10KB data.

It would be nice to do this with two transfers:

- a 5-byte transfer in tx, composed by

1 command byte

3 address byte

1 dummy byte - another transfer with 10KB rx buffer, and NULL tx buffer

obviously the chip-select must be asserted at the first transfer and de-asserted at the end of the second transfer, between the two transfers the chip-select must remain asserted. In other words CONT must be 1 and CONTC 0 in the first transfer. While in the second transfer both CONT and CONTC must be 1. At the end of the second transfer CONTC shoud be written 0 to deassert CS. Obviously only one TCR write must be made between the two transactions.

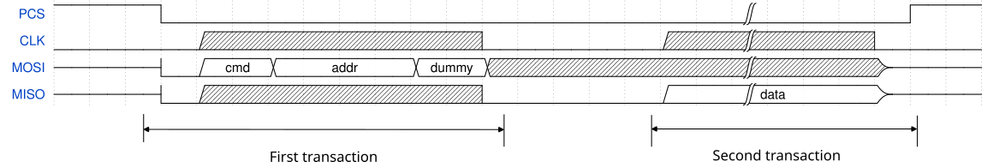

I tried to draw a time diagram to explain myself better:

In the first transaction I only write, in the second transaction I only read, but between the two the PCS must remain asserted.

I am using SDK 2.15.000, how can I achieve this behavior using API of SDK?

You may ask why do I need this? A single call to LPSPI_MasterTransferBlocking() would force me to allocate both rxData and txData buffers with two vectors of more than 10KB, in which the tx buffer is completely useless. Is exactly what I would like to avoid.

Note that some years ago I asked the same question, but did not get a satisfactory answer.

best regards

Max

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

I agree with the previous response, I suggest you use LPSPI_MasterTransferNonBlocking() since it has a handle that allows you to configure the bytes to receive/transmit.

In continuous mode, there are some known issues so you can opt to use PCS as GPIO to have control on it. Details on this issue are found here: Solved: RT1050 LPSPI last bit not completing in continuous mode - NXP Community

Best regards,

Omar