- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- I2S channel swapping

I2S channel swapping

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I2S channel swapping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are using 4 LPC5526 FlexComm modules with shared clocks to handle 4 bidirectional audio channels. We have found that the DMA flips left and right channels intermittently. Has anyone seen this problem before?

We are wondering if we should try using the SCT module to hardware trigger the DMAs using the shared WS signal.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your help. We need to run I2S in slave mode as the LRCLK (WS) and SCLK are synchronized to the external digital audio signals. It seems like we can get this running on the right channels for hours, but then it will intermittently flip the channels. Any other ideas?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Regarding your question that "it will intermittently flip the channels", I have not good idea. If you have found out that the left/right channels are swapped, you can delete a sample or add a sample to correct the swap.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We can not detect when the error occurs. We see that the data is in the correct channel when loaded into the buffer before the DMA transfers the ping or pong buffer to the peripheral. We do not understand what is causing the problem from there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi.

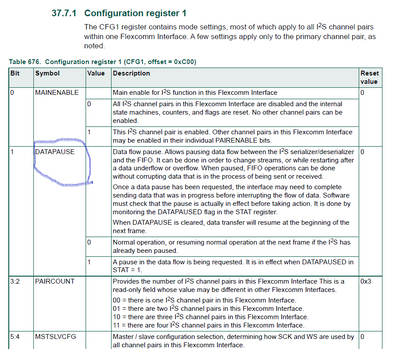

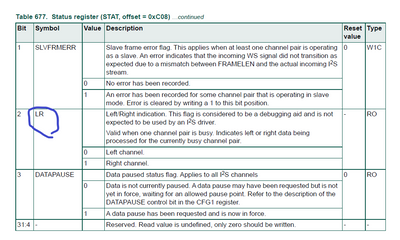

I think it is complicated why the left/right channels are swapped, for example, the FIFO overflowing or under-flowing all can lead to the channel swap. you can set the PAUSEDATA bit in CFG1 register, then poll the PAUSEDATA bit in status register, then clear the PAUSEDATA bit in CFG1 register to correct the swap.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For LPC552x, you use the I2S in master mode, both the left and right channels use the same FIFO FIFOWR, so you can not identify or control which channel you will write.

There is a flag in I2S status register, which can reflect the current channel, but the flag is only used in debugger instead of driver.

Hope it can help you

BR

XiangJun Rong