- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: Hw trigger ADC using CT timers

Hw trigger ADC using CT timers

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Hw trigger ADC using CT timers

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am using the LPC55s69 Dev kit

I need to configure the ADC to be triggered from an CT timers. and then the DMA to copy the data to RAM.

I am using the SDK 2.6.3.

whats needed:use an CT as a HW trigger and have the dma automatically copying data into a Ram buffer.

Any help would be appreciated

Regards,

Sushant Kulkarni

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Need to convert sw triggered sdk example to hw trigger . please provide configuration and other chnages required .

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Sushant,

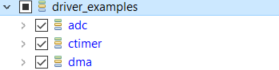

There are Ctimer, ADC and DMA demos under SDK, you can refer to.

BTW, recommend you use the latest version of SDKv2.7.1.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

continue from above mail:

Also do i need to enable Interrupt or callback function

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello sushant ,

- Please first try to use software trigger ADC, whether it can work well?

- If software trigger can work, set the EMC3 of Timer external match registers(EMR) to 0x2.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear @Alice_Yang ,

you suggest to set EMC3 (in the external match register EMR of the timer) to 0x2. This bit means "Set the corresponding External Match bit/output EM3 to 1". Thus when a match occurs between the TC and MR3, the EM3 bit is set and generates the corresponding ADC trigger (if enabled).

However, the manual also states "hardware trigger events are detected on the rising-edge of the associated hardware trigger source.". Thus until the EM3 bit in EMC is reset, no further hardware trigger through CTIMER will occur.

How do you suggest to handle this problem? Reset EM3 bit through ADC ISR?

Instead, I've set EMC3 to 0x3, that is "Toggle EM3 bit". This triggers ADC on every other timer cycle: The first timer match sets the EM3 bit which in turn generates the ADC hardware trigger. The next timer match resets the EM3 bit. This effectively reduces the trigger frequency by 2.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Alice,

I am modifying existing lpadc_dma example provided with SDK

i checked all peripheral ADC, Ctimer and DMA individually. problem is with integration of all three.

I have configured following:

ADC:

enabled hardware trigger 5

5 State Counter Timer (CTIMER) ct0_mat3_out via TCTRLa[HTEN] for index 5

TCTRLa[TPRI] is kept 0

Ctimer:

#define CTIMER CTIMER0 /* Timer 0 */

#define CTIMER_MAT_OUT kCTIMER_Match_3 /* Match output 3 */

#define CTIMER_CLK_FREQ CLOCK_GetCTimerClkFreq(2U)

config:

matchConfig.enableCounterReset = true;

matchConfig.enableCounterStop = false;

matchConfig.matchValue = CTIMER_CLK_FREQ / 4;

matchConfig.outControl = kCTIMER_Output_Toggle;

matchConfig.outPinInitState = true;

matchConfig.enableInterrupt = false;

CTIMER_SetupMatch(CTIMER, CTIMER_MAT_OUT, &matchConfig);

DMA :

No modification from Lpadc_dma example.

Changes in main:

Removed getchar() and LPADC_DoSoftwareTrigger(). and called CTIMER_StartTimer(CTIMER) before while(1)

my understanding:

i/p: continious square wave from function generator on P28 on board

As the ctimer value reaches the matchvalue , CTIMER_MAT_OUT (which is mat_out_3) performs togle operation and reloads timer .

mat_out_3 rising edge acts as hardware trigger to ADC and after conversion it should trigger DMA to transfer from FIFO to ram .

but not able to see output in FIFO or ram variable . so ADC is not triggered .

Please do tell if any configuration is missing or function call to be done in main.