- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: Processor Expert External Interrupt Component

Processor Expert External Interrupt Component

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Processor Expert External Interrupt Component

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The processor I am using is the MK22FN256VLH12. A GPIO bit in a Port is configured

as an Input which will interrupt on both edges of the signal.The ExtInt component is

used to configure the interrupts. An ExtInt_Ldd has been built with an Initialization

function, the Interrupt handler, and the GetVal function. I use the GetVal to determine

which edge caused the interrupt.

First the Initialization function in ExtInt_LDD is never called, is this correct?

My main problem is the first time that an interrupt is generated my ISR is entered

at the function's entry point. However, the next interrupt results in the ISR being entered

in the middle of the function.Is this a result of the data structure not being initialized?

What can I do to make this work correctly?

I must have had a brain freeze. What I need to do is have 1 ISR which checks which pin caused

the interrupt and processes accordingly. I apologize for wasted time.

SORRY - The problem description is incorrect. My reply to Robin describes the problem that I am having.

I was relying on Breakpoints that did not trigger.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Richard,

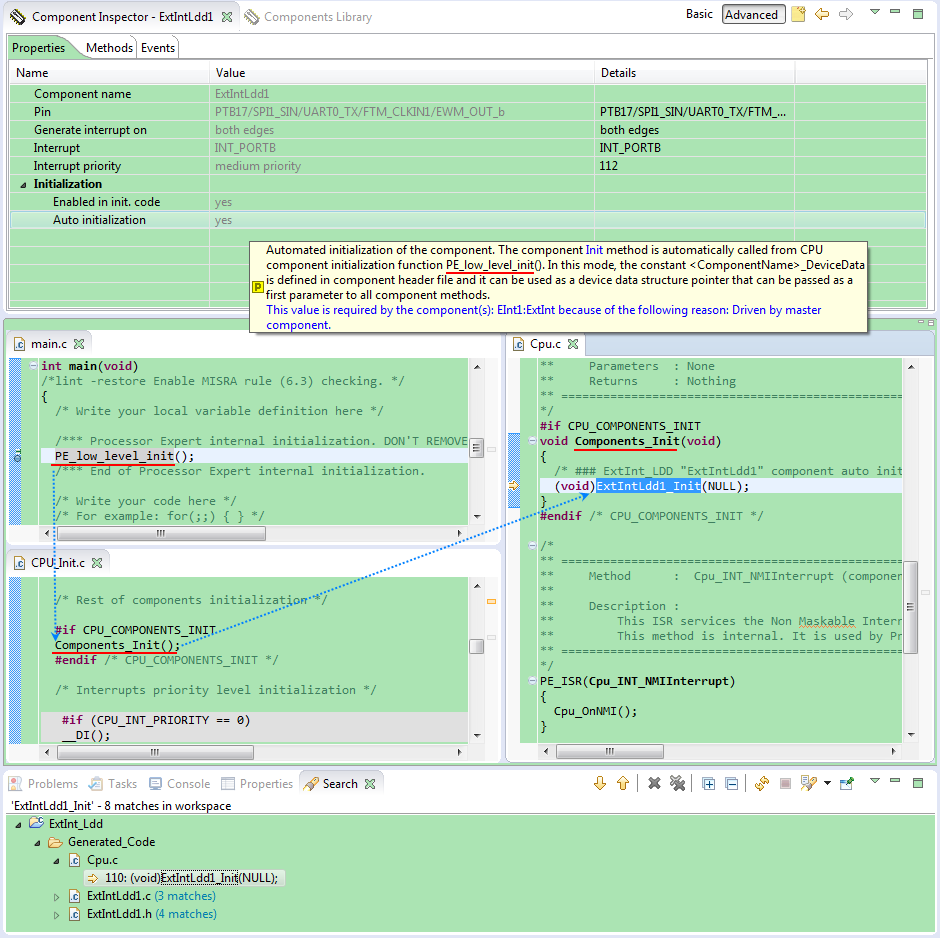

The initialization function is called in my project.(See the attached image)

I'm not very clear about: "My main problem is the first time that an interrupt is generated my ISR is entered at the function's entry point. However, the next interrupt results in the ISR being entered in the middle of the function."

Could you please attach these two images?

Best Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Robin,

Sorry, the problem description in my post is incorrect. I went through the generated code this

morning, and see what is actually happening.

I am using 2 GPIOs in Port B to determine if a switch has been pressed. The first GPIO is for

on row in the switch matrix. The second GPIO is for another row (a different set of switches).

I have both GPIOs configured to interrupt on both edges of the switch press. The two GPIOs

should be independent. The first GPIO uses ExtLdd2, while the second one uses ExtLdd3.

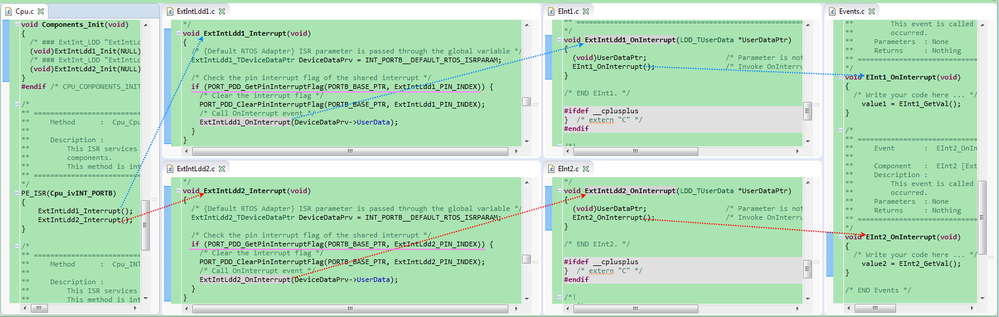

I expected that there would be two distinct ISRs for the Ports. However, the CPU component

has set up both of the external interrupt components as one.

PE_ISR(Cpu_ivINT_PORTB)

{

ExtIntLdd2_Interrupt();

ExtIntLdd3_Interrupt();

}

So the first of my ISRs falls into the second ISR.

Somehow I need to have Processor Expert assign two different interrupt vectors for the two

components.Probably something that I misconfigured.

Regards,

Richard

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Richard,

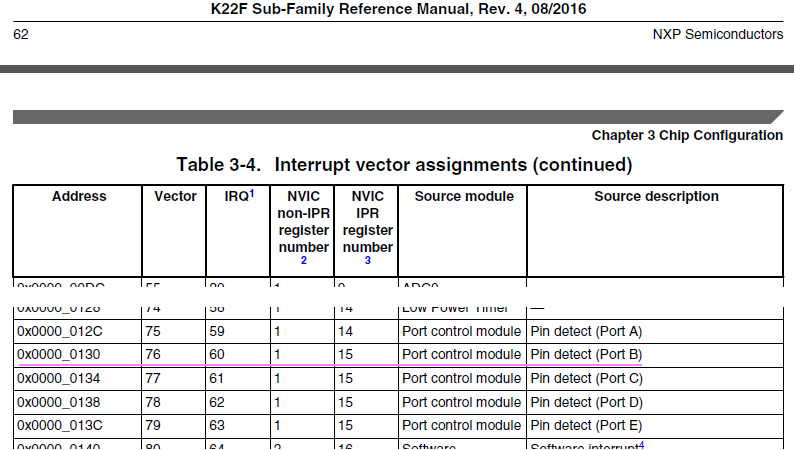

All Ports have their own ISR(interrupt vector). If you need to have Processor Expert assign two different interrupt vectors for the two components, please use two different Ports.(for example:one GPIO in Port B and the other GPIO in Port C)

If you using 2 GPIOs in Port B, the code will "Check the pin interrupt flag of the shared interrupt" to determine which switch caused the PE_ISR(Cpu_ivINT_PORTB).

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Robin,

Thanks for your input. I have the code working. I just needed to

understand

how the generated code functioned.

Dick Fox

Firmware Engineer

NATIONAL CONTROLS CORPORATION BUSINESS UNIT

INSTRUMENTATION AND SPECIALTY CONTROLS DIVISION

1725 Western Dr | West Chicago, IL 60185 | http://www.ametekncc.com

Phone: (630)621-3118 | email: Dick Fox@ametek.com

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Richard,

Which "generated code" do you want to understand? Do you mean PE_ISR(Cpu_ivINT_PORTB)?

The ISF bit in PORTx_PCRn is used to determine which GPIO caused the interrupt of Port B. You can see the code(pink line) in attached image at my last reply. If the interrupt is caused by ExtIntLdd2_Interrupt, the code will still run into ExtIntLdd1_Interrupt to check the pin interrupt flag(ISF of PORTx_PCRn) first. And then run into ExtIntLdd2_Interrupt to chenk the the second pin interrupt flag.

If you still need to have Processor Expert assign two different interrupt vectors for the two components? The Port B has only one interrupt vector, all the GPIOs in Port B share this interrupt vector. So if you still need two different interrupt vectors for the two components, you need to use two GPIOs in different Port.

Best Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Robin,

I don't need help understanding the code. After I looked at the

code I understood how it worked. My program is working. Thanks

for your assistance.

Dick Fox

Firmware Engineer

NATIONAL CONTROLS CORPORATION BUSINESS UNIT

INSTRUMENTATION AND SPECIALTY CONTROLS DIVISION

1725 Western Dr | West Chicago, IL 60185 | http://www.ametekncc.com

Phone: (630)621-3118 | email: Dick Fox@ametek.com