- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- [MKW01Z128] SPI communication - Master

[MKW01Z128] SPI communication - Master

[MKW01Z128] SPI communication - Master

Hello everyone,

first off, I'm new to this website and programming. I have a problem with SPI communication on MKW01Z128. I will try to give you as much details as possible.

I am using IAR ide. I took KSDK example from MRB KW01 chip since it was the closest name to my chip. My chip will be the master of this communication. I configured SPI pins(in fuction void configure_spi_pins(uint32_t instance)) in pin_mux correctly:

PORT_HAL_SetMuxMode(PORTE,0u,kPortMuxAlt2); /* MISO */

PORT_HAL_SetMuxMode(PORTE,1u,kPortMuxAlt2); /* MOSI */

PORT_HAL_SetMuxMode(PORTD,5u,kPortMuxAlt2); /* SCK */

PORT_HAL_SetMuxMode(PORTD,4u,kPortMuxAlt2); /* PCS0 */

for pin 27, 29, 32, 34 as SPI1 PCS, SPI1 clock, SPI1 MISO, SPI1 MOSI on my chip.

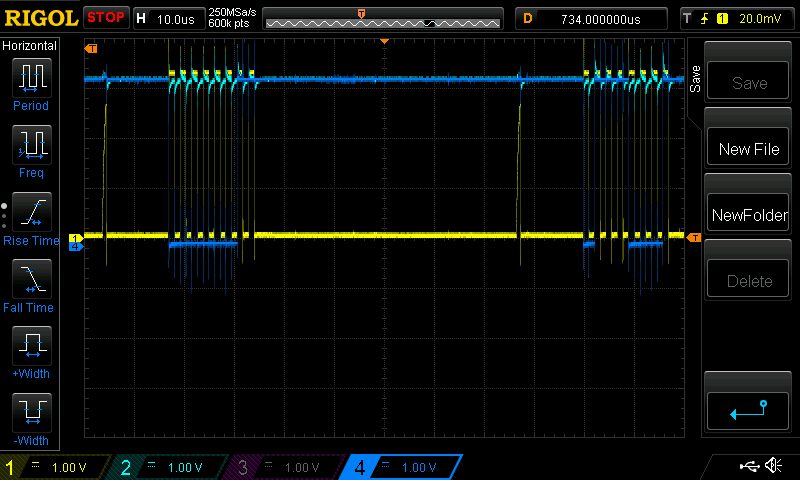

Everything works fine, except a wierd short clock pulse(in yellow- MOSI is dark blue and MISO is light blue) everytime I send a packet before the actual payload:

A closeup of this short pulse:

MOSI sends correct bits and clock works great except the pulse part.

Unfortunatelly this pulse messes up the slave so won't send his data back. Tested this SPI communication with some other chip and it worked fine.

I will paste my code for inicialization and sending packets as well, maybe that is the cause:

#define SPI_MASTER_INSTANCE BOARD_SPI_INSTANCE /*! User change define to choose SPI instance */

#define TRANSFER_BAUDRATE (1250000U) /*! Transfer baudrate - 500k */

#define MASTER_TRANSFER_TIMEOUT (100U) /*! Transfer timeout of master - 100ms */uint32_t calculatedBaudRate;

spi_master_state_t spiMasterState;

spi_master_user_config_t userConfig =

{

#if FSL_FEATURE_SPI_16BIT_TRANSFERS

.bitCount = kSpi8BitMode,

#endif

.polarity = kSpiClockPolarity_ActiveHigh,

.phase = kSpiClockPhase_SecondEdge,

.direction = kSpiMsbFirst,

.bitsPerSec = TRANSFER_BAUDRATE

};

//CLOCK_SYS_EnablePortClock(PORTA_IDX); //doesn't matter

CLOCK_SYS_EnablePortClock(PORTD_IDX);

CLOCK_SYS_EnablePortClock(PORTE_IDX);

// dbg_uart_init();

configure_spi_pins(SPI1_IDX);

// Init OSA layer.

OSA_Init();

// Init and setup baudrate for the master

SPI_DRV_MasterInit(SPI_MASTER_INSTANCE, &spiMasterState);

SPI_DRV_MasterConfigureBus(SPI_MASTER_INSTANCE,

&userConfig,

&calculatedBaudRate);

and sending packets:

if (SPI_DRV_MasterTransferBlocking(SPI_MASTER_INSTANCE, NULL, SendBuffer, s_spiSinkBufferS, 5, MASTER_TRANSFER_TIMEOUT) == kStatus_SPI_Timeout){}

I also tried normal(non-blocking) sending of packets, but clock still does this pulse.

If anyone has any questions or information about it I would appreaciate the comment.

Thank you in advance, Erik

Hello Erik,

Which evaluation board and demo application are you using? In case you are using the FRDM-KW01, there is a board support patch for KSDK 1.3 under the Archive Releases section in the KSDK page. This patch adds support for the FRDM-KW01 board, including the set of demos and examples, into an existing KSDK 1.3.0 installation.

Regards,

Gerardo