- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: Issue with MDIO (k60DN512)

Issue with MDIO (k60DN512)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Issue with MDIO (k60DN512)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Everyone,

I am using K60DN512 device with Lan8720A phy device.

I have initialized the Ethernet MAC, but there is no data on MDIO pin (I have checked on logic analyser)

I have done following initialization.

GPIO

SIM ->SCGC5 |= SIM_SCGC5_PORTA_MASK | SIM_SCGC5_PORTB_MASK;

//Configure RMII0_RXER (PTA5)

PORTA ->PCR[5] = PORT_PCR_MUX(4) | PORT_PCR_PE_MASK;

//Configure RMII0_RXD1 (PTA12)

PORTA ->PCR[12] = PORT_PCR_MUX(4);

//Configure RMII0_RXD0 (PTA13)

PORTA ->PCR[13] = PORT_PCR_MUX(4);

//Configure RMII0_CRS_DV (PTA14)

PORTA ->PCR[14] = PORT_PCR_MUX(4);

//Configure RMII0_TXEN (PTA15)

PORTA ->PCR[15] = PORT_PCR_MUX(4);

//Configure RMII0_TXD0 (PTA16)

PORTA ->PCR[16] = PORT_PCR_MUX(4);

//Configure RMII0_TXD1 (PTA17)

PORTA ->PCR[17] = PORT_PCR_MUX(4);

//Configure RMII0_MDIO (PTB0)

PORTB ->PCR[0] = PORT_PCR_MUX(4) | PORT_PCR_PE_MASK | PORT_PCR_PS_MASK;

//Configure RMII0_MDC (PTB1)

PORTB ->PCR[1] = PORT_PCR_MUX(4);

GPIO is configured as alternate function 4, as mentioned in datasheet.

Next disabled the IRQ

| //Disable Ethernet MAC interrupts |

NVIC_DisableIRQ(ENET_Transmit_IRQn);

NVIC_DisableIRQ(ENET_Receive_IRQn);

NVIC_DisableIRQ(ENET_Error_IRQn);

Next initialized the MAC

//Enable ENET peripheral clock

SIM ->SCGC2 |= SIM_SCGC2_ENET_MASK;

//GPIO configuration

mk60EthInitGpio(interface);

//Reset ENET module

ENET ->ECR = ENET_ECR_RESET_MASK;

//Wait for the reset to complete

while (ENET ->ECR & ENET_ECR_RESET_MASK)

;

//Reveive control register

ENET ->RCR = ENET_RCR_MAX_FL(1518) | ENET_RCR_RMII_MODE_MASK

| ENET_RCR_MII_MODE_MASK;

//Transmit control register

ENET ->TCR = 0;

//Configure MDC clock frequency

ENET ->MSCR = ENET_MSCR_MII_SPEED(19);

Next read the first SFR of the Phy device.

uint32_t value = ENET_MMFR_ST(1) | ENET_MMFR_OP(2) | ENET_MMFR_TA(2);

//PHY address

value |= ENET_MMFR_PA(phyAddr);

//Register address

value |= ENET_MMFR_RA(regAddr);

//Clear MII interrupt flag

ENET ->EIR = ENET_EIR_MII_MASK;

//Start a read operation

Bit1_SetVal(NULL);

ENET ->MMFR = value;

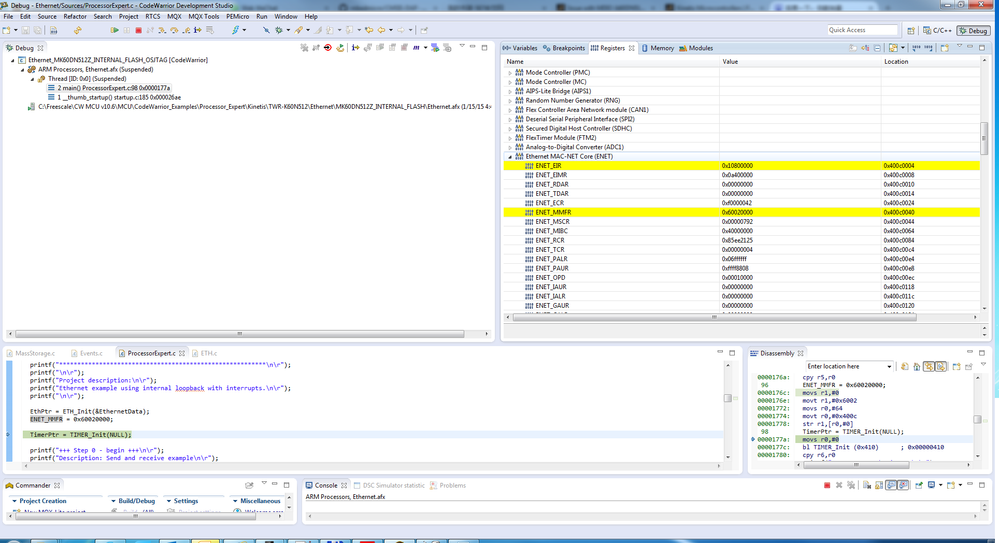

In the last line, the value comes out to be 0x60020000 (TA = 10 ... This field must be programmed to 10 to generate a valid MII management frame.), when it executes the value of MMFR is 0x60030000 (TA=11). Why is this happening.

I think all the values are initialized correctly. When I checked on logic analyser, there is no output. However as soon as I execute the command, the MII interrupt flag of EIR is set.

I tried changing the value of TA to 10 (In debug mode, through the register view), but it simply doesn't work.

Is there something wrong with the initialization. I have not connected the CAT cable, but I feel that shouldn't make any difference.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Just some more suggestion, Since you are using RMII mode for your application, then 50MHz should be feed to the Enet module, so the internal MAC clock frequency is 50MHz as well, and according to RM, The MII_SPEED field in ENET_MSCR must be programmed with a value to provide an MDC frequency of less than or equal to 2.5 MHz to be compliant with the IEEE 802.3 MII specification. RM recommends 0x9 for the case of 50MHz, here you used 19 so will have a 1.25MHz MDC clock, not sure if that is the root cause, but you may try to adjust the value as below to see if it makes any difference.

ENET_MSCR = ENET_MSCR_HOLDTIME(0x07) |

ENET_MSCR_DIS_PRE_MASK |

ENET_MSCR_MII_SPEED(0x09);

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I have same issue, done all clock register configuration correctly but I'm unable to get the clock of less than or equal to 2.5Mhz. On MDC pin I'm getting around 4.1 Mhz. And able to read raw packets on wire-shark! getting some random packets/frames.

Please help me out

Thank you

Trilok

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Chaitannya & Kan Li,

Did you find a solution to this issue? I am having a similar issue. The TA bits of the MMFR register are always set to 3 even though I set them to 2 in software as well as in the debugger.

We are using a Kinetis K61, a 83848 phy device and I am using MQX on my project but the problem is the same. I did see that ENET_MSCR_MII_SPEED in my design was being set to 18 and I changed it to 9 but this did not fix anything. Any information that you could offer would be a help.

Thanks,

Dan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Found my issue. The 83848 phy device defaults to an address of 1 and MQX defaults to 0. Don't know why this affects setting of the TA bits, but after changing BSP_ENET0_PHY_ADDR to the correct address all is well.

-Dan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am sorry, but I can not reproduce your issue on TWR-K60N512, you may find the MMFR is 0x60020000 after the write operation, and I provided a code snippet for Enet initialization for your reference, please kindly refe to it for details.

/* ===================================================================*/

LDD_TDeviceData* ETH_Init(LDD_TUserData *UserDataPtr)

{

ETH_TDeviceData *DeviceDataPrv;

ETH_TTxQueueItem *TxQueueItemPtr;

ETH_TRxQueueItem *RxQueueItemPtr;

uint8_t* MemPtr;

/* Allocate internal device data structure */

/* {Default RTOS Adapter} Driver memory allocation: Dynamic allocation is simulated by a pointer to the static object */

DeviceDataPrv = &DeviceDataPrv__DEFAULT_RTOS_ALLOC;

DeviceDataPrv->DuplexMode = LDD_ETH_FULL_DUPLEX; /* Store duplex mode configuration */

DeviceDataPrv->FilterMode = LDD_ETH_ACCEPT_BC; /* Store filter mode configuration */

DeviceDataPrv->SleepMode = LDD_ETH_DISABLED; /* Store sleep mode configuration */

DeviceDataPrv->UserDataPtr = UserDataPtr; /* Store the RTOS device structure */

DeviceDataPrv->Index = 0U; /* Set the component instance index */

DeviceDataPrv->EventMask = /* Initialize the event mask */

LDD_ETH_ON_FRAME_TRANSMITTED |

LDD_ETH_ON_FRAME_RECEIVED |

LDD_ETH_ON_FATAL_ERROR |0U;

DeviceDataPrv->EnabledMode = TRUE; /* Enable the device clock configuration */

/* SIM_SCGC2: ENET=1 */

SIM_SCGC2 |= SIM_SCGC2_ENET_MASK;

ENET_PDD_DisableDevice(ENET_BASE_PTR);

DeviceDataPrv->Enabled = FALSE;

ENET_PDD_EnableMIBCounters(ENET_BASE_PTR, FALSE); /* Disable statistic counters */

ENET_PDD_ClearMIBCounters(ENET_BASE_PTR); /* Clear statistic counters */

ENET_PDD_EnableMIBCounters(ENET_BASE_PTR, TRUE); /* Enable statistic counters */

/* Set pin assignments */

/* PORTB_PCR1: ISF=0,MUX=4 */

PORTB_PCR1 = (uint32_t)((PORTB_PCR1 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x03)

)) | (uint32_t)(

PORT_PCR_MUX(0x04)

));

/* PORTB_PCR0: ISF=0,MUX=4 */

PORTB_PCR0 = (uint32_t)((PORTB_PCR0 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x03)

)) | (uint32_t)(

PORT_PCR_MUX(0x04)

));

/* PORTA_PCR18: ISF=0,MUX=0 */

PORTA_PCR18 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* PORTA_PCR16: ISF=0,MUX=4 */

PORTA_PCR16 = (uint32_t)((PORTA_PCR16 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x03)

)) | (uint32_t)(

PORT_PCR_MUX(0x04)

));

/* PORTA_PCR17: ISF=0,MUX=4 */

PORTA_PCR17 = (uint32_t)((PORTA_PCR17 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x03)

)) | (uint32_t)(

PORT_PCR_MUX(0x04)

));

/* PORTA_PCR15: ISF=0,MUX=4 */

PORTA_PCR15 = (uint32_t)((PORTA_PCR15 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x03)

)) | (uint32_t)(

PORT_PCR_MUX(0x04)

));

/* PORTA_PCR14: ISF=0,MUX=4 */

PORTA_PCR14 = (uint32_t)((PORTA_PCR14 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x03)

)) | (uint32_t)(

PORT_PCR_MUX(0x04)

));

/* PORTA_PCR13: ISF=0,MUX=4 */

PORTA_PCR13 = (uint32_t)((PORTA_PCR13 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x03)

)) | (uint32_t)(

PORT_PCR_MUX(0x04)

));

/* PORTA_PCR12: ISF=0,MUX=4 */

PORTA_PCR12 = (uint32_t)((PORTA_PCR12 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x03)

)) | (uint32_t)(

PORT_PCR_MUX(0x04)

));

/* Set interrupt priorities */

/* NVICIP76: PRI76=0x80 */

NVICIP76 = NVIC_IP_PRI76(0x80);

/* NVICISER2: SETENA|=0x1000 */

NVICISER2 |= NVIC_ISER_SETENA(0x1000);

/* NVICIP77: PRI77=0x80 */

NVICIP77 = NVIC_IP_PRI77(0x80);

/* NVICISER2: SETENA|=0x2000 */

NVICISER2 |= NVIC_ISER_SETENA(0x2000);

/* NVICIP78: PRI78=0x80 */

NVICIP78 = NVIC_IP_PRI78(0x80);

/* NVICISER2: SETENA|=0x4000 */

NVICISER2 |= NVIC_ISER_SETENA(0x4000);

/* Set interrupt mask */

/* ENET_EIMR: ??=0,BABR=0,BABT=0,GRA=0,TXF=1,TXB=0,RXF=1,RXB=0,MII=0,EBERR=1,LC=0,RL=0,UN=0,PLR=0,WAKEUP=0,TS_AVAIL=0,TS_TIMER=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

ENET_EIMR = (ENET_EIMR_TXF_MASK | ENET_EIMR_RXF_MASK | ENET_EIMR_EBERR_MASK);

/* Clear interrupt flags */

/* ENET_EIR: ??=1,BABR=1,BABT=1,GRA=1,TXF=1,TXB=1,RXF=1,RXB=1,MII=1,EBERR=1,LC=1,RL=1,UN=1,PLR=0,WAKEUP=0,TS_AVAIL=0,TS_TIMER=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

ENET_EIR = ENET_EIR_BABR_MASK |

ENET_EIR_BABT_MASK |

ENET_EIR_GRA_MASK |

ENET_EIR_TXF_MASK |

ENET_EIR_TXB_MASK |

ENET_EIR_RXF_MASK |

ENET_EIR_RXB_MASK |

ENET_EIR_MII_MASK |

ENET_EIR_EBERR_MASK |

ENET_EIR_LC_MASK |

ENET_EIR_RL_MASK |

ENET_EIR_UN_MASK |

0x80000000U;

/* Allocate the transmit frame interrupt vector */

/* {Default RTOS Adapter} Set interrupt vector: IVT is static, ISR parameter is passed by the global variable */

INT_ENET_Transmit__DEFAULT_RTOS_ISRPARAM = DeviceDataPrv;

/* Allocate the receive frame interrupt vector */

/* {Default RTOS Adapter} Set interrupt vector: IVT is static, ISR parameter is passed by the global variable */

INT_ENET_Receive__DEFAULT_RTOS_ISRPARAM = DeviceDataPrv;

/* Allocate the shared interrupt vector */

/* {Default RTOS Adapter} Set interrupt vector: IVT is static, ISR parameter is passed by the global variable */

INT_ENET_Error__DEFAULT_RTOS_ISRPARAM = DeviceDataPrv;

/* Set MAC address */

/* ENET_PALR: PADDR1=0x06FFFFFF */

ENET_PALR = ENET_PALR_PADDR1(0x06FFFFFF);

/* ENET_PAUR: PADDR2=0xFFFF,TYPE=0 */

ENET_PAUR = (ENET_PAUR_PADDR2(0xFFFF) | ENET_PAUR_TYPE(0x00));

/* Set unicast address hash table */

/* ENET_IAUR: IADDR1=0 */

ENET_IAUR = ENET_IAUR_IADDR1(0x00);

/* ENET_IALR: IADDR2=0 */

ENET_IALR = ENET_IALR_IADDR2(0x00);

/* Set multicast address hash table */

/* ENET_GAUR: GADDR1=0 */

ENET_GAUR = ENET_GAUR_GADDR1(0x00);

/* ENET_GALR: GADDR2=0 */

ENET_GALR = ENET_GALR_GADDR2(0x00);

/* Set PAUSE frame duration */

/* ENET_OPD: OPCODE=0,PAUSE_DUR=0 */

ENET_OPD = (ENET_OPD_OPCODE(0x00) | ENET_OPD_PAUSE_DUR(0x00));

/* Set transmit control register */

/* ENET_TCR: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,CRCFWD=0,ADDINS=0,ADDSEL=0,RFC_PAUSE=0,TFC_PAUSE=0,FDEN=1,??=0,GTS=0 */

ENET_TCR = (ENET_TCR_ADDSEL(0x00) | ENET_TCR_FDEN_MASK);

/* Set transmit accelerator function configuration register */

/* ENET_TACC: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,PROCHK=0,IPCHK=0,??=0,??=0,SHIFT16=0 */

ENET_TACC = 0x00U;

/* Set receive control register */

/* ENET_RCR: GRS=0,NLC=0,MAX_FL=0x05EE,CFEN=0,CRCFWD=0,PAUFWD=1,PADEN=0,??=0,??=0,RMII_10T=0,RMII_MODE=1,??=0,??=0,FCE=1,BC_REJ=0,PROM=0,MII_MODE=1,DRT=0,LOOP=1 */

ENET_RCR = ENET_RCR_MAX_FL(0x05EE) |

ENET_RCR_PAUFWD_MASK |

ENET_RCR_RMII_MODE_MASK |

ENET_RCR_FCE_MASK |

ENET_RCR_MII_MODE_MASK |

ENET_RCR_LOOP_MASK;

/* Set receive accelerator function configuration register */

/* ENET_RACC: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,SHIFT16=0,LINEDIS=0,??=0,??=0,??=0,PRODIS=0,IPDIS=0,PADREM=0 */

ENET_RACC = 0x00U;

/* Set transmit inter-packet gap */

/* ENET_TIPG: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,IPG=8 */

ENET_TIPG = ENET_TIPG_IPG(0x08);

/* Set frame truncation length */

/* ENET_FTRL: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,TRUNC_FL=0x0800 */

ENET_FTRL = ENET_FTRL_TRUNC_FL(0x0800);

/* Set transmit FIFO watermark */

/* ENET_TFWR: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,STRFWD=1,??=0,??=0,TFWR=0 */

ENET_TFWR = (ENET_TFWR_STRFWD_MASK | ENET_TFWR_TFWR(0x00));

/* Set transmit FIFO section empty threshold */

/* ENET_TSEM: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,TX_SECTION_EMPTY=0 */

ENET_TSEM = ENET_TSEM_TX_SECTION_EMPTY(0x00);

/* Set transmit FIFO almost empty threshold */

/* ENET_TAEM: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,TX_ALMOST_EMPTY=8 */

ENET_TAEM = ENET_TAEM_TX_ALMOST_EMPTY(0x08);

/* Set transmit FIFO almost full threshold */

/* ENET_TAFL: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,TX_ALMOST_FULL=8 */

ENET_TAFL = ENET_TAFL_TX_ALMOST_FULL(0x08);

/* Set receive FIFO section full threshold */

/* ENET_RSFL: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,RX_SECTION_FULL=0 */

ENET_RSFL = ENET_RSFL_RX_SECTION_FULL(0x00);

/* Set receive FIFO section empty threshold */

/* ENET_RSEM: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,RX_SECTION_EMPTY=0 */

ENET_RSEM = ENET_RSEM_RX_SECTION_EMPTY(0x00);

/* Set receive FIFO almost empty threshold */

/* ENET_RAEM: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,RX_ALMOST_EMPTY=8 */

ENET_RAEM = ENET_RAEM_RX_ALMOST_EMPTY(0x08);

/* Set receive FIFO almost full threshold */

/* ENET_RAFL: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,RX_ALMOST_FULL=8 */

ENET_RAFL = ENET_RAFL_RX_ALMOST_FULL(0x08);

/* Set MII speed control register */

/* ENET_MSCR: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,HOLDTIME=7,DIS_PRE=1,MII_SPEED=9,??=0 */

ENET_MSCR = ENET_MSCR_HOLDTIME(0x07) |

ENET_MSCR_DIS_PRE_MASK |

ENET_MSCR_MII_SPEED(0x09);

/* Set receive buffer size */

/* ENET_MRBR: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,R_BUF_SIZE=0x0B,??=0,??=0,??=0,??=0 */

ENET_MRBR = ENET_MRBR_R_BUF_SIZE(0x0B);

/* Initialize the transmit frame buffer queue */

LDD_QUEUE_INIT(ETH_TTxQueueItem, DeviceDataPrv->TxQueue, ETH_QUEUE_MEM_ALIGN); /* Initialize the queue data structure */

TxQueueItemPtr = LDD_QUEUE_GET_DATA_START(DeviceDataPrv->TxQueue);

while (TxQueueItemPtr != (LDD_QUEUE_GET_DATA_END(DeviceDataPrv->TxQueue) + 1)) {

/* Clear queue item */

for (MemPtr = (uint8_t*)(uint32_t)TxQueueItemPtr; MemPtr != (uint8_t*)(uint32_t)(TxQueueItemPtr + 1); MemPtr++) {

*MemPtr = 0U;

}

TxQueueItemPtr++; /* Move to the next queue item */

}

setReg32(ENET_TDSR, LDD_QUEUE_GET_DATA_START(DeviceDataPrv->TxQueue));

/* Initialize the receive frame buffer queue */

LDD_QUEUE_INIT(ETH_TRxQueueItem, DeviceDataPrv->RxQueue, ETH_QUEUE_MEM_ALIGN); /* Initialize the queue data structure */

RxQueueItemPtr = LDD_QUEUE_GET_DATA_START(DeviceDataPrv->RxQueue);

while (RxQueueItemPtr != (LDD_QUEUE_GET_DATA_END(DeviceDataPrv->RxQueue) + 1)) {

/* Clear queue item */

for (MemPtr = (uint8_t*)(uint32_t)RxQueueItemPtr; MemPtr != (uint8_t*)(uint32_t)(RxQueueItemPtr + 1); MemPtr++) {

*MemPtr = 0U;

}

RxQueueItemPtr++; /* Move to the next queue item */

}

setReg32(ENET_RDSR, LDD_QUEUE_GET_DATA_START(DeviceDataPrv->RxQueue));

/* ENET_ECR: ??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,STOPEN=0,DBGEN=1,??=0,EN1588=0,SLEEP=0,MAGICEN=0,ETHEREN=0,RESET=0 */

ENET_ECR = ENET_ECR_DBGEN_MASK;

/* Enable the device */

ENET_PDD_EnableDevice(ENET_BASE_PTR);

DeviceDataPrv->Enabled = TRUE;

/* Registration of the device structure */

PE_LDD_RegisterDeviceStructure(PE_LDD_COMPONENT_ETH_ID,DeviceDataPrv);

return (LDD_TDeviceData*)DeviceDataPrv;

}

you may refer to the example in "C:\Freescale\CW MCU v10.6\MCU\CodeWarrior_Examples\Processor_Expert\Kinetis\TWR-K60N512\Ethernet" for more details.

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kan

I have same issue I'm using RMII mode and external clock is 50Mhz, but on MDC signal getting around 4.55Mhz. Please can you tell me exact problem.

thank you

Trilok