- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

PT60 WDOG in emulation CW

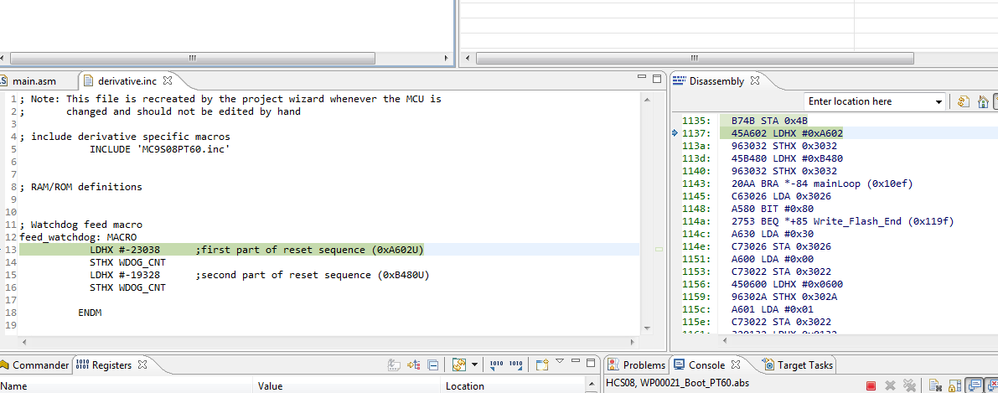

Dear all, I have a MC9S08PT60, I develop the application with CodeWarrior Development Studio Version: 10.3 and USB Multilink.

feed_watchdog: MACRO

LDHX #-23038 ;first part of reset sequence (0xA602U)

STHX WDOG_CNT

LDHX #-19328 ;second part of reset sequence (0xB480U)

STHX WDOG_CNT

ENDM

I have inizialized the WDOG with:

ldhx #$C520

sthx WDOG_CNT

ldhx #$D928

sthx WDOG_CNT

movx #$04, WDOG_TOVAL

movx #$00, WDOG_CS2

movx #$80, WDOG_CS1

cli

mainLoop:

nop

feed_watchdog

bra mainLoop

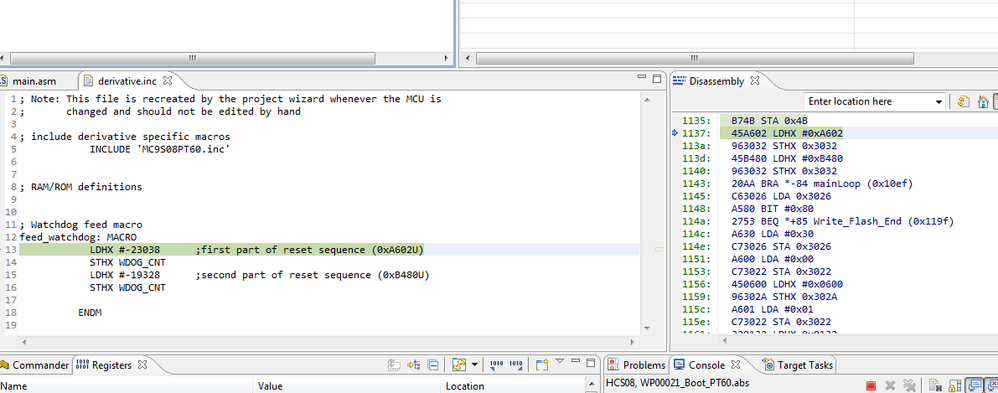

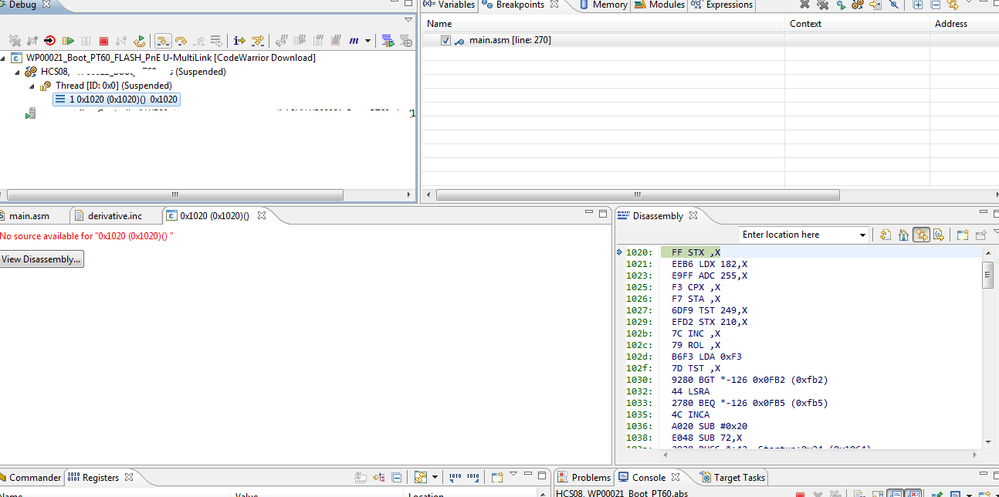

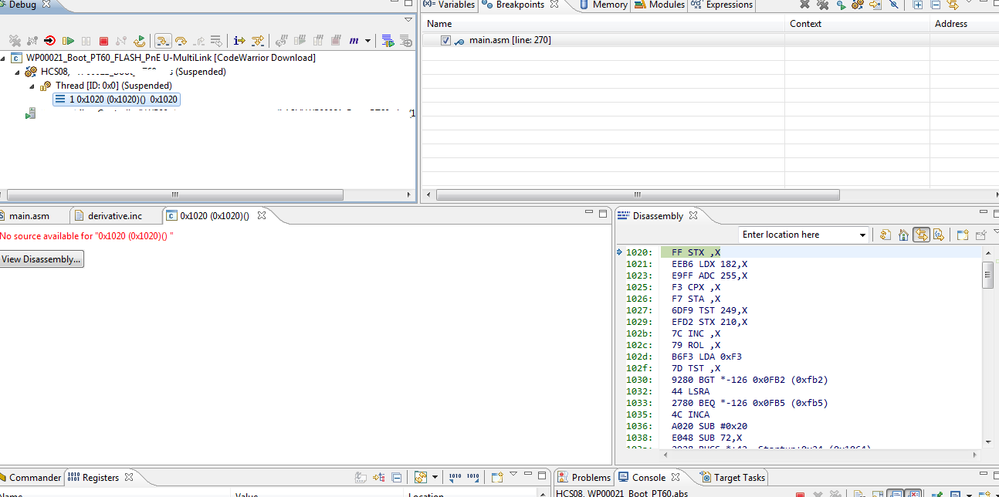

The problem is when I Suspend the excution and go by step, when execute the sthx WDOG_Cnt instruction the execution goes at random address !!

After the next 2 step:

How can i solve this problem ?

Thanks

Stefano

HI

you should never step through these sequences, allways go over and keep this atomic, there is limit of just few bus clks see the related info from ref manual below

Pavel

------------------------

23.3.1.2 Refreshing the Watchdog

The refresh write sequence is a write of 0xA602 followed by a write of 0xB480 to the

WDOG_CNTH:L registers. The write of the 0xB480 must occur within 16 bus clocks

after the write of 0xA602; otherwise, the watchdog resets the MCU.

Before starting the refresh sequence, disable global interrupts.

Otherwise, an interrupt could effectively invalidate the refresh

sequence if writing the four bytes takes more than 16 bus

clocks. Re-enable interrupts when the sequence is finished.

23.3.1.3 Example code: Refreshing the Watchdog

The following code segment shows the refresh write sequence of the WDOG module.

/* Refresh watchdog */

for (;;) // main loop

{

...

DisableInterrupts; // disable global interrupt

WDOG_CNT = 0xA602; // write the 1st refresh word

WDOG_CNT = 0xB480; // write the 2nd refresh word to refresh counter

EnableInterrupts; // enable global interrupt

...

}

Thanks, Pavel,

Yes, I followed all that religiously, and got an immediate [WDOG, RESET, Illegal Opcode, Illegal Address, etc] interrupt on the first write when I stepped through it. With the option to enable WDOG in chip debug mode, I assumed stepping through would be OK, especially since the clock source is the bus clk. I'll take your advice and just run through that process.

Thanks,

lm