- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

Hello?

Based on imx8mm-evk board, I'm trying to control IC with connecting through ecspi2 ports of "EXP CN" attached.

After adding some codes imx8mm-evk.dts like the below, updated imx8mm-evk.dtb on boot disc, but there's no any "spi device" on directory, "/dev".

Could anyone help to resolve this?

&ecspi2 {

#address-cells = <1>;

#size-cells = <0>;

fsl,spi-num-chipselects = <1>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi2>;

cs-gpios = <&gpio5 13 GPIO_ACTIVE_LOW>;

status = "okay";

spidev1: spi@0 {

reg = <0>;

compatible = "rohm,dh2228fv";

spi-max-frequency = <500000>;

};

};

pinctrl_ecspi2: ecspi2grp {

fsl,pins = <

MX8MM_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK 0x19 //0x11

MX8MM_IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI 0x19 //0x11

MX8MM_IOMUXC_ECSPI2_MISO_ECSPI2_MISO 0x19 //0x11

>;

};

已解决! 转到解答。

Hi,

You can refer to imx8mn-evk.dts.

See below, please!

pinctrl_ecspi2: ecspi2grp {

fsl,pins = <

MX8MM_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK 0x82

MX8MM_IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI 0x82

MX8MM_IOMUXC_ECSPI2_MISO_ECSPI2_MISO 0x82

>;

};

pinctrl_ecspi2_cs: ecspi2cs {

fsl,pins = <

MX8MM_IOMUXC_ECSPI2_SS0_GPIO5_IO13 0x40000

>;

};

......

&ecspi2 {

#address-cells = <1>;

#size-cells = <0>;

fsl,spi-num-chipselects = <1>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi2 &pinctrl_ecspi2_cs>;

cs-gpios = <&gpio5 13 GPIO_ACTIVE_LOW>;

status = "okay";

spidev0: spi@0 {

reg = <0>;

compatible = "rohm,dh2228fv";

spi-max-frequency = <500000>;

};

};

Have a nice day!

B.R,

weidong

Hi

I got the result of the below.

SPI stack is alive but not working.

SW: rel_imx_5.4.47_2.2.0

HW: imx8mm EVK Board,

The below is Imx8mm-evk.dts

&ecspi2 {

#address-cells = <1>;

#size-cells = <0>;

fsl,spi-num-chipselects = <1>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi2 &pinctrl_ecspi2_cs>;

cs-gpios = <&gpio5 13 GPIO_ACTIVE_LOW>;

status = "okay";

spidev@0 {

reg = <0>;

compatible = "spidev";

spi-max-frequency = <500000>; //<100000>;

};

};

pinctrl_ecspi2: ecspi2grp {

fsl,pins = <

MX8MM_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK 0x82 //0x175 //0x00001916 //0x11

MX8MM_IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI 0x82 //0x175 //00000116 //0x11

MX8MM_IOMUXC_ECSPI2_MISO_ECSPI2_MISO 0x82 //0x175 // 00000116 //0x1

>;

};

pinctrl_ecspi2_cs: ecspi2cs {

fsl,pins = <

MX8MM_IOMUXC_ECSPI2_SS0_GPIO5_IO13 0x40000

>;

}

- Spi node : created “spidev1.0” in “/dev” folder

- Loopback : Connect SDI & SDO directly , pin 19 & 21 of EXP CN(attached)

- Refet to EXP CN Page 13, “SPF-31407_C2 EVK-BASE Board Circuit .pdf”

- Test : $ ./spidev_test -v -D /dev/spidev1.0 (the result is attached)

- The value of CLK, DSO, & SS ports never changed.

root@imx8mmevk:/run/media/mmcblk1p3# ./spidev_test -v -D /dev/spidev1.0

spi mode: 0x0

bits per word: 8

max speed: 500000 Hz (500 KHz)

TX | FF FF FF FF FF FF 40 00 00 00 00 95 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF F0 0D |......@.........................|

RX | 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................................|

Refer to result “dmesg | grep spi”

root@imx8mmevk:/run/media/mmcblk1p3# dmesg | grep spi

[ 1.354391] spi_imx 30830000.spi: registered master spi1

[ 1.354503] spi spi1.0: spi_imx_setup: mode 1, 8 bpw, 1000000 hz

[ 1.354512] spi spi1.0: setup mode 1, 8 bits/w, 1000000 Hz max --> 0

[ 1.354772] spi_imx 30830000.spi: registered child spi1.0

[ 1.354778] spi_imx 30830000.spi: probed

[ 1.359164] imx8mm-pinctrl 30330000.pinctrl: pin MX8MM_IOMUXC_NAND_ALE already requested by 30830000.spi; cannot claim for 30bb0000.spi

[ 1.371350] imx8mm-pinctrl 30330000.pinctrl: pin-61 (30bb0000.spi) status -22

[ 1.378498] imx8mm-pinctrl 30330000.pinctrl: could not request pin 61 (MX8MM_IOMUXC_NAND_ALE) from group flexspi0grp on device 30330000.pinctrl

[ 1.391459] nxp-fspi 30bb0000.spi: Error applying setting, reverse things back

[ 1.398697] nxp-fspi: probe of 30bb0000.spi failed with error -22

[ 51.841387] spidev spi1.0: spi_imx_setup: mode 0, 8 bpw, 1000000 hz

[ 51.841399] spidev spi1.0: setup mode 0, 8 bits/w, 1000000 Hz max --> 0

[ 51.841403] spidev spi1.0: spi mode 0

[ 51.841413] spidev spi1.0: spi_imx_setup: mode 0, 8 bpw, 1000000 hz

[ 51.841423] spidev spi1.0: setup mode 0, 8 bits/w, 1000000 Hz max --> 0

[ 51.841426] spidev spi1.0: 8 bits per word

[ 51.841436] spidev spi1.0: spi_imx_setup: mode 0, 8 bpw, 500000 hz

[ 51.841442] spidev spi1.0: setup mode 0, 8 bits/w, 500000 Hz max --> 0

[ 51.841699] spi_imx 30830000.spi: mx51_ecspi_clkdiv: fin: 50000000, fspi: 500000, post: 3, pre: 12

[ 75.901686] spidev spi1.0: spi_imx_setup: mode 0, 8 bpw, 1000000 hz

[ 75.901699] spidev spi1.0: setup mode 0, 8 bits/w, 1000000 Hz max --> 0

[ 75.901704] spidev spi1.0: spi mode 0

[ 75.901713] spidev spi1.0: spi_imx_setup: mode 0, 8 bpw, 1000000 hz

[ 75.901722] spidev spi1.0: setup mode 0, 8 bits/w, 1000000 Hz max --> 0

[ 75.901726] spidev spi1.0: 8 bits per word

[ 75.901735] spidev spi1.0: spi_imx_setup: mode 0, 8 bpw, 500000 hz

[ 75.901741] spidev spi1.0: setup mode 0, 8 bits/w, 500000 Hz max --> 0

[ 75.902104] spi_imx 30830000.spi: mx51_ecspi_clkdiv: fin: 50000000, fspi: 500000, post: 3, pre: 12

[ 149

I got..

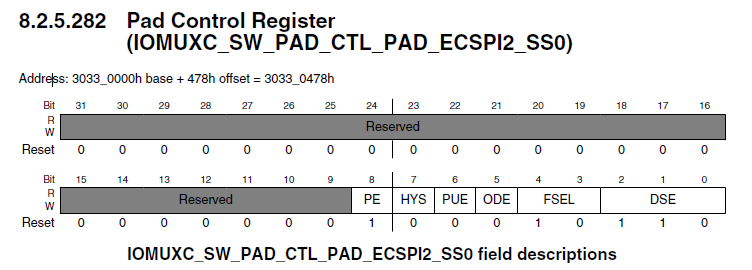

"The last integer CONFIG is the pad setting value like pull-up on this pin. Please refer to i.MX8M Mini Reference Manual for detailed CONFIG settings."

"8.2.5.279 Pad Control Register"

(IOMUXC_SW_PAD_CTL_PAD_ECSPI2_SCLK)

Thanks!

BR

Weidong

Hi, Weidong

On the imx8mm-evk board for new project, I just copied a spi codes from imx7ulp.dts used in an old project.

so I'm not sure that "dh2228fv" chip is used or not in the EVK board. so it should be changed. (I'm a complete novice at Linux)

I realized there's some setting issues in imx8mm-evk.dts through "dmesg | grep spi" and "booting messages", so I'm trying to find a solution through reading related documents and manual.

I don't know what "xxxx" means in the below codes.

(?? initial values or setting values in a register )

Could you let me give any reference related about the usage ?

Thank you in advance.

------------------

pinctrl_ecspi2: ecspi2grp {

fsl,pins = <

MX8MM_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK "xxxx"

MX8MM_IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI "xxxx"

MX8MM_IOMUXC_ECSPI2_MISO_ECSPI2_MISO "xxxx"

MX8MM_IOMUXC_ECSPI2_SS0_ECSPI2_SS0 "xxxx"

>;

};

Hi,

You can refer to imx8mn-evk.dts.

See below, please!

pinctrl_ecspi2: ecspi2grp {

fsl,pins = <

MX8MM_IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK 0x82

MX8MM_IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI 0x82

MX8MM_IOMUXC_ECSPI2_MISO_ECSPI2_MISO 0x82

>;

};

pinctrl_ecspi2_cs: ecspi2cs {

fsl,pins = <

MX8MM_IOMUXC_ECSPI2_SS0_GPIO5_IO13 0x40000

>;

};

......

&ecspi2 {

#address-cells = <1>;

#size-cells = <0>;

fsl,spi-num-chipselects = <1>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi2 &pinctrl_ecspi2_cs>;

cs-gpios = <&gpio5 13 GPIO_ACTIVE_LOW>;

status = "okay";

spidev0: spi@0 {

reg = <0>;

compatible = "rohm,dh2228fv";

spi-max-frequency = <500000>;

};

};

Have a nice day!

B.R,

weidong

I'm having similar issues to what is described in this forum thread. I've been spending several days trying to get the escpi2 on the imx8 work, by having the imx-spi.c and spi.c linux drivers use the chip select SS0 line configured for GPIO5_IO13. I've seen similar configuration settings used in several other NXP posts to configure the chip select (CS) for escpi2.

Can you please explain the line:

MX8MM_IOMUXC_ECSPI2_SS0_GPIO5_IO13 0x40000

The 0x40000 sets reserved bit 18.

Can you please provide a definition for bit 18 ?

Are there any other secret reserved bits that exist in this register?

Can you please update the documentation to describe these secret reserved bits ?

I also tried to use the i.MX_CFG_v12 Config Tools for i.MX Version 12 and was unable to find my answer there.