- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- programming addresses bigger then 24bit in nor flash with flexSPI

programming addresses bigger then 24bit in nor flash with flexSPI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

programming addresses bigger then 24bit in nor flash with flexSPI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all!

I am using my modified SDK example of the flexSPI_nor_polling_transfer example code.

I am trying to program an external 32MB flash chip.

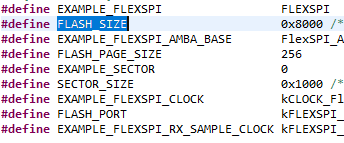

I have changed the flash size definition in the code:

I noticed that when I reach the address 0x100 0000 and above I actually reach address 0x0.

I think I cannot program or read addresses bigger then 24bit

how can I fix this ?

thanks

Adi

Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

NXP never ever fully answers this repeated question on this forum. When NXP? When?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

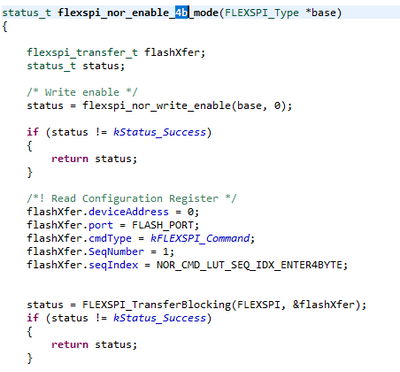

I have add this to LUT:

and with the function:

but its not effective

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

From my point of view, 32MB should be accessed

For your question, i have an idea here.

I supposed you are using 3BYTE address mode, but for the address bigger than 3BYTE(bingger than 0x100 0000), you cannot get the correct data. So i thinks you should use 4BYTE address mode access the space bigger than 0x100 0000.

You can read the flash datasheet to know how to use 4BYTE mode and update the LUT in RT device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

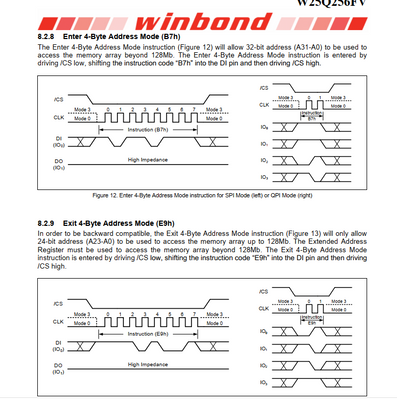

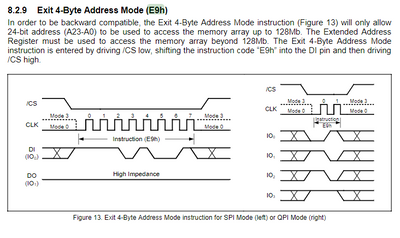

this is from the data sheet:

if i only need to add values to the LUT table, which should I add?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @adi2Intel ,

Please refer to the Look Up Table section in reference manual. The bit number is the operand value in instruction code. For example,

// Read LUTs

[0] = FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0xEB, RADDR_SDR, FLEXSPI_4PAD, 0x18),

[1] = FLEXSPI_LUT_SEQ(DUMMY_SDR, FLEXSPI_4PAD, 0x06, READ_SDR, FLEXSPI_4PAD, 0x04),

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@adi2Intel could you please let us know if changing that 0x18 (24) to 0x20 (32) in the LUT is sufficient to make W25Q256FV flash to work? I suspect the answer is NO because according to 6.1.5 in datasheet, to operate in 4-bytes addressing mode ADP bit in Status Register must be set, but factory default value for it is 0.

Please also pay attention to what you wrote in the LUT, according to the datasheet 0xE9 command is EXIT 4-byte addressing mode, not ENTER.

Let us know, please. Thanks!