- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- DCDC converter output stabilisation issue IMXRT1020EVK

DCDC converter output stabilisation issue IMXRT1020EVK

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

DCDC converter output stabilisation issue IMXRT1020EVK

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi All

We are doing some reliability testing and have identified a potential issue when testing on the MIMXRT1020EVK with regard to the DCDC converter.

The test consists of starting code that configures the DCDC to allow operation at 500MHz (setting 1.25V), running further code testing USB device operation and commanding a SW core reset so that the test repeats every (approx) 2s.

Typically after a few hundred such cycles the DCDC converter stabilising check spins for a long time, causing WDOG3 (used to monitor such issues) to fire and a further reset to be executed, after which it continues again normally. When the test is run for 2500 cycles the issue is seen maybe 10..15 times (to give an idea of its frequency).

The code is

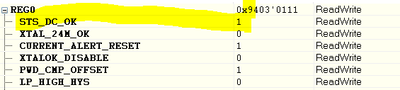

DCDC_REG3 = ((DCDC_REG3 & ~DCDC_REG3_TRG_MASK) | DCDC_REG3_TRG_1_250V); // increase the DCDC voltage from default 1.15V to 1.25V

while ((DCDC_REG0 & DCDC_REG0_STS_DC_OK) == 0) { } // wait until the DCDC output stabilises

If WDOG3 timeout is set to a high value (like 30s) the hang is noticed and the attached debugger can be paused (it is in the while loop). The core registers show that the DCDC_REG0_STS_DC_OK was '0' when it was last checked but when the DCDC_REG0 register is viewed it is displayed as set.

Although the debugger can read registers, single stepping no longer works so it may be that the issue also has an effect on some other operation so it can't be known for sure that the DCDC stabilised and the code could continue or not.

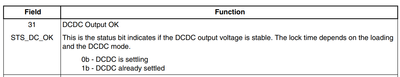

The definition of the flag shows that the stabilisation is HW dependent:

but there is no further information about what is expected.

Since this happens on the MIMXRT1020EVK it may also be circuit design dependent and not happen on all HW.

Comments are welcome since this is very reproducible and somewhat worrying (although the WDOG3 does seem to always allow recovery after a delay).

Regards

Mark

For i.MX and Kinetis stock availability see https://www.utasker.com/Shop/semi.html

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @mjbcswitzerland ,

How did you implement the test code? is it just something like GPIO initialization and WDOG3 initialization with the following code in the end?

DCDC_REG3 = ((DCDC_REG3 & ~DCDC_REG3_TRG_MASK) | DCDC_REG3_TRG_1_250V); // increase the DCDC voltage from default 1.15V to 1.25V

while ((DCDC_REG0 & DCDC_REG0_STS_DC_OK) == 0) { } // wait until the DCDC output stabilises

Please kindly clarify.

Have a great day,

Kan

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Yes, this is the case

1. Set GPIO

2. Configure Watchdog

3. Change the DC/DC voltage <------------ sometimes hangs

4. Increase frequency from default to 528MHz

5. Start application code

6. After 2s command SW reset so it restarts at 1. again

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @mjbcswitzerland ,

Thanks for the clarification! Is it possible to share the code? I will try to reproduce it here, not sure if it is a board specific issue.

Have a great day,

Kan

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I have managed a fairly good improvement with the following change:

Originally the DCDC converter voltage change was performed in a single step:

DCDC_REG3 = ((DCDC_REG3 & ~DCDC_REG3_TRG_MASK) | DCDC_REG3_TRG_1_250V); // increase the DCDC voltage from default 1.15V to 1.25V

_WAIT_REGISTER_FALSE(DCDC_REG0, DCDC_REG0_STS_DC_OK); // wait until the DCDC output stabilises

but if it is instead performed in several small steps:

DCDC_REG3 = ((DCDC_REG3 & ~DCDC_REG3_TRG_MASK) | DCDC_REG3_TRG_1_175V);

_WAIT_REGISTER_FALSE(DCDC_REG0, DCDC_REG0_STS_DC_OK); // wait until the DCDC output stabilises

DCDC_REG3 = ((DCDC_REG3 & ~DCDC_REG3_TRG_MASK) | DCDC_REG3_TRG_1_200V);

_WAIT_REGISTER_FALSE(DCDC_REG0, DCDC_REG0_STS_DC_OK); // wait until the DCDC output stabilises

DCDC_REG3 = ((DCDC_REG3 & ~DCDC_REG3_TRG_MASK) | DCDC_REG3_TRG_1_225V);

_WAIT_REGISTER_FALSE(DCDC_REG0, DCDC_REG0_STS_DC_OK); // wait until the DCDC output stabilises

DCDC_REG3 = ((DCDC_REG3 & ~DCDC_REG3_TRG_MASK) | DCDC_REG3_TRG_1_250V); // increase the DCDC voltage from default 1.15V to 1.25V

_WAIT_REGISTER_FALSE(DCDC_REG0, DCDC_REG0_STS_DC_OK); // wait until the DCDC output stabilises

the chance that it hangs waiting for a change to complete is reduced. Yesterday, after 2500 resets it got stuck (and the watchdog triggered) just twice.

I do however note that if the test has been running already for a long time the chance of it getting stuck seems to be reduced too - maybe something that is temperature dependent?

I have attached a binary that runs on the MIMXRT1020EVK. If the USB device cable is connected to a hist it will reset each time the USB enumerates (so there is a beep every approx. 2s). When the problem occurs it is noticeable due to the beep stopping for a few seconds (the WDOG is set to 4s).

After each restart there is output on the debug interface (the board's CDC UART connection) which shows the number of resets that have been tested and the overall time of operation:

Hello, world... MIMXRT1020 [Software 508 (1)] <----- 508 SW resets + (1) WDOG reset

Unique ID: 0x65f824a41b2119d2-50000004

01.01.1970 00:21:21 <---- time since the EVK was powered on

Static memory = 0x00000878

OS Heap use = 0x000003d5 from 0x00011000

Initial stack margin 0x0001e5b8

FlexRAM:

2 Code banks [0x00000000..0x0000ffff]

6 Data banks [0x20000000..0x2002ffff]

SPI Flash: ISSI 8MByte IS25LP032A

I will repeat the test on some other EVKs to see whether there is a difference in their reliability with respect to the DCDC configuration.

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Looks like MIMXRT1060EVK is free of the issue:

Hello, world... MIMXRT1060 [Software 3005] <----------3005 SSW resets counted

Unique ID: 0x65f82946453849d2-500000ff

01.01.1970 02:13:55 <--- in 2hrs 13 minutes

Static memory = 0x000008c8

OS Heap use = 0x000003d5 from 0x0002b000

Initial stack margin 0x00044568

FlexRAM:

2 Code banks [0x00000000..0x0000ffff]

14 Data banks [0x20000000..0x2006ffff]

SPI Flash: ISSI 8MByte IS25LP032A

>3000 sw resets without it hanging on the DCDC configuration.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Looks like MIMXRT1024EVK is free of the issue (although I only tested for about 1 hour)

Hello, world... MIMXRT1024 [Software 1780] <----------1780 SW resets counted

Unique ID: 0x677efb092d3a19d2-50000030

01.01.1970 00:55:22 <--- in 55 minutes

Static memory = 0x00000878

OS Heap use = 0x000003d5 from 0x0000a000

Initial stack margin 0x000255b8

FlexRAM:

2 Code banks [0x00000000..0x0000ffff]

6 Data banks [0x20000000..0x2002ffff]

SPI Flash: Winbond 4MByte W25Q32