- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Clocking SAI1 from SPDIF on rt1052

Clocking SAI1 from SPDIF on rt1052

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Clocking SAI1 from SPDIF on rt1052

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We would like to clock the SAI subsystem from the received SPDIF signal.

I did some experimenting with the clocking and routed the SPDIF SR_CLOCK to SAI1_MCLK3 and then selected MCLK3 for bit clock generation for SAI1. This kind of works, the bit clock and sync clock are generated based on the SR_CLOCK, with correct frequencies, but the audio in the SAI gets chopped up.

The SAI subsystem works correctly with bit clock generated from the SAI1_CLOCK_ROOT.

I have 2 observations when we use the SPDIF SR_CLOCK:

1- The generated bit clock has a small amount of jitter

2- The master clock and the bit clock are not synchronous.

Can anyone advise on a proper way to clock the SAI peripheral from the SPDIF receive line.

Thank you in advance,

Best Regars,

Veselin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VeselinK ,

Thanks you for your interest in the NXP MIMXRT product, I would like to provide service for you.

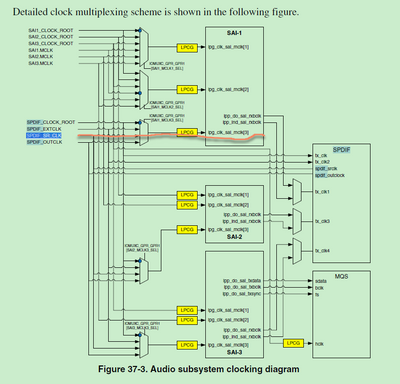

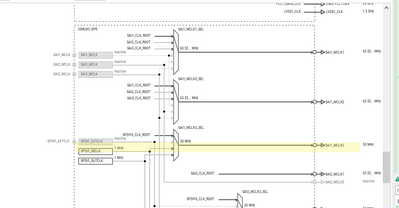

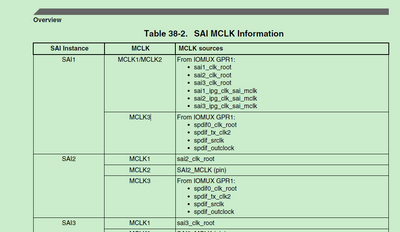

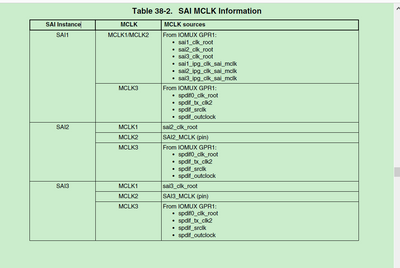

I think you use this method:

Right?

If your SAI TX BCLK already select as the SAI1 MCLK3 which is the SPDIF_SR_CLK, then your meet issues is caused by your mentioned jitter, your MCLK is not clean, it cases the SAI abnormal, as you know, the BCLK is derive from the MCLK, if MCK have issues, the BCLK may have issues.

So, you must need to make sure your MCLK is clean from the hardware side, then test it again.

After that, if you still meet the bit clock are not synchronous issues, you need to check the SAI module configuration, you can use the CFG peripheral to configure it.

Wish it helps you!

Best Regards,

kerry

PS: BTW, from Jan.29th to Feb 6th is our Chinese Spring Festival(Chinese New Year), so if you have any updated information, I may reply you later, thanks a lot for your understanding.

But, if you are urgent, you can create a new case at that time, as we also have colleague located in Mexico still can provide service for you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kerryzhou ,

Hope you had a festive and relaxing holiday!

I am using the method you have shown above, SPDIF_SR_CLK used as source for SAI1 MCLK3, and selecting MCLK3 as bit clock source.

I am still facing the jitter issue, I have tried inputting a very clean SPDIF signal from an "SR1 Audio Analyzer" but the bit clock is still jittering. I also tried taking the SPDIF OUT which is clocked by the internal audio PLL, and inputting that in the SPDIF IN but the issue is still the same.

The SPDIF subsystem always reports that we have a lock on the signal (LOCK bit = 1).

The issue persists on all sample rates as well.

In the reference manual it is stated that the SR_CLK is measured in reference to the system clock, which in this case is the IPG_CLK with 150MHz frequency, could the IPG_CLK be at fault in some way?

Do you have any recommendations on what to try to pinpoint the problem ?

Best Regards,

Veselin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VeselinK

Thanks you for your updated information.

The jitter still from SPDIF_SR_CLK, which is the output the SPDIF RX clock pin, right?

Do you have some wave about it?

I have a question, whether you can choose other internal clock as SAI1 MCLK3, which is the same frequency as the SPDIF_SR_CLK?

Could you please also give me some photos of your connection? whether jitter is from the SPDIF_SR_CLK pin connection directly? Do you connect something in the SPDIF_SR_CLK pin externally?

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kerryzhou ,

The jitter is from the SAI1 bit clock pin. I have attached a photo of the bit clock on the scope .

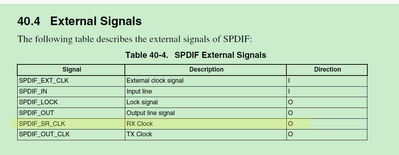

The SPDIF_SR_CLK pin (L12) is not actually routed on our board so I cannot measure on that.

About the routing something else on MCLK3, I guess I could route the clk_root (00 option), i will give you feedback about that.

I have another question on a connected topic:

The sai1_mclk on pin M13 is the SAI1_clk_root correct?

Is it possible to route a different clock to that pin? For instance route SPDIF_SR_CLK to SAI1_MCLK3 and then route MCLK3 to the MCLK pin, I could not find an option like this.

Best Regards,

Veselin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VeselinK ,

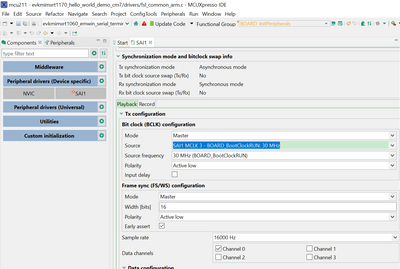

The audio master clock generates the bit clock when the receiver or transmitter is

configured for an internally generated bit clock.

So, now, your bit clock have jitter, please use the internal master clock to test it again.

I think you can use the sai_clk_root directly from MCLK1/MCLK2.

Then select the related MCLK option to test it, whether the bit clock still have jitter or not?

If you have the MIMXRT1050-EVKB board, you even can test the SDK sai project directly.

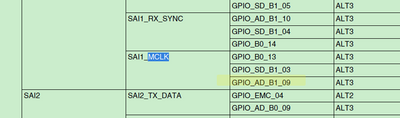

About the pins, yes, M13 is the master clock pin, it is GPIO_AD_B1_09, but you need to configure it.

Config the pin in the pinmux.c.

IOMUXC_SetPinMux(IOMUXC_GPIO_AD_B1_09_SAI1_MCLK, 1U);

IOMUXC_SetPinConfig(IOMUXC_GPIO_AD_B1_09_SAI1_MCLK, 0x10B0U);

The SDK is using this pin.

You can try it on your side.

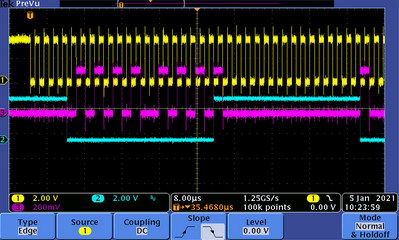

BTW, I also checked my previous SAI wave, in fact my BCLK also have small jitter:

But, it didn't meet any sai data transfer issues.

The yellow is the BCLK, and the MCLK is from the internal side.

Wish it helps you!

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kerryzhou ,

When using an internal clock there is no jitter on the bit clock.

From the testing I did I don't think the jitter is causing the issue I have, which is the following.

I have the SAI1 sub-system working, its used in master mode and it drives an ADC and a DAC. I have no issue with that, I use the audio pll (pll4) for root clock and all the clocks are fine. But we want to clock the ADC and DAC from the SPDIF. I can use the SPDIF SR clock to generate a bit clock and sync clock, and that is also ok, but the master clock going to the ADC and DAC is not in sync with the two other clocks, even if I measure the frequencies and get them very close they always drift apart. So I think I need the master clock going to the DAC and ADC to also be clocked from the SPDIF and not internally, so all the clocks can be synchronous and in phase.

One test I did is taking a cable and connecting the SPDIF IN and OUT on the imx, the SPDIF OUT is clocked by PLL4 internally, so the SR clock that is being generated from the input is synchronous with the master clock, then everything works, otherwise when all 3 clocks are not in sync the audio from the DAC/ADC gets chopped up.

The master clock select fields change only the source for the bit clock, but not the master clock coming out of the IMX itself.

Have I missed something?

Best Regards,

Veselin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VeselinK ,

MCLK also can output the pin, do you test when you use the internal PLL or the external clock, which difference of the MCLK?

You mentioned the SPDIF OUT is clocked by PLL4 internally, then it works, otherwise, it can't work,

Could you please tell me this otherwise, which clock you are using for the SPDIF out?

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kerryzhou ,

I have no issue with the SPDIF OUT, the issue I have is with the external DAC and ADC. You mentioned we can output a different clock on the MCLK pin. Can you explain how to do that?

Best Regards

Veselin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VeselinK ,

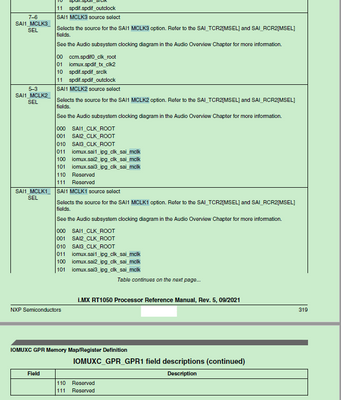

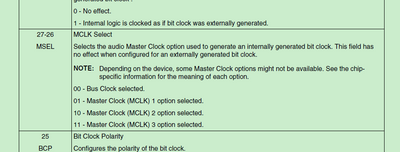

As My previous reply list, MCLK also can select through the IOMUXC_GPR_GPR1 register.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @kerryzhou ,

I have tried using GPR1 register to change the mclk, but this does not change the output on the MCLK pin.

Best Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VeselinK ,

Thanks for your updated information.

Which MCLK you have modified?

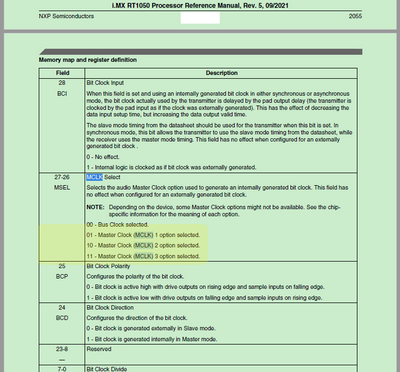

In the SAI module TCR2, you also need to select your modified MCLK, otherwise, you can't find the change in MCLK pin.

Wish it helps you!

Best Regards,

Kerry