- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi All

Due to a rapid product development/production requirement I have been forced to purchase a large quantity of (old) i.MX RT 1052 with silicon revision A0. These have some errata that need to be worked around in HW by ensuring power sequencing timing and driving the DCDC_IN/DCDC_IN_Q at a reduced voltage level.

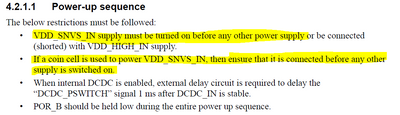

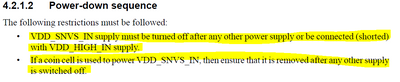

However the ERR011092 workaround throws up a question since it states that the workaround is to apply the DCDC_IN/DCDC_IN_Q power supply 1ms ahead of VDD_SNVS_IN. This is in contradiction to the general data sheet that specifies:

and

Presumably the workaround takes priority in the first case but how can it be applied after DCDC_IN/DCDC_INQ is there is a backup battery always connected?

Specifically, does this workaround actually state that a back-up battery cannot be used (no RTC) or is it not relevant if a battery backup is supplying VDD_SNVS_IN all the time?

If a design wants to use the RTC with battery backup would it mean that the input DCDC cannot be used and an external 1V1 VDD_SOC_IN supply is needed instead?

Many thanks in advance for an exact answer that will allow the design to be completed without risks of the errata problems being present in the product.

Regards

Mark

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) If a design wants to use the RTC with battery backup would it mean that the input DCDC cannot be used and an external 1V1 VDD_SOC_IN supply is needed instead?

-- Yes, the workaround is in contradiction to the general power-up sequence, and I'd highly recommend you bypass the DCDC if use the RTC with battery backup to avoid any risk.

Hope it helps.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) If a design wants to use the RTC with battery backup would it mean that the input DCDC cannot be used and an external 1V1 VDD_SOC_IN supply is needed instead?

-- Yes, the workaround is in contradiction to the general power-up sequence, and I'd highly recommend you bypass the DCDC if use the RTC with battery backup to avoid any risk.

Hope it helps.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

OK - thanks

Based on this information confirming that battery back-up and DCDC are not possible together on the A0 revision devices the battery backup function will not be used and external RTC with battery backed up memory will be used instead - this allows the use of the internal DCDC with the power sequencing workarounds in place.

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @jeremyzhou

Could you please have a quick look at these two related posts?

https://community.nxp.com/t5/i-MX-RT/Large-current-surge-problem-during-power-sequencing-of-i-MX-RT/...

https://community.nxp.com/t5/i-MX-RT/No-USB-ISP-Operation-on-i-MX-RT-1052A/m-p/1325836#M15937

The present state is that when following the workaround it has not yet been possible to get the board to operate - the first describes the large current surges that are being seen when powering with the sequences as advised and the second describes the fact the neither SWD nor ISP modes then work (although the processor does access the QSI Flash and the HS USB low level is operating).

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告