- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- RT1052 ADC function in low power run mode

RT1052 ADC function in low power run mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I run into an issue of the ADC which doesn't work in low power run mode (all PLLs are disabled except for PLL2 bypass 24M XTALOSC, core runs at 24MHz frequency), but it's fine in full speed mode. I thought some settings of ADC clock might be incorrect. Having tried different clock sources (ADACK and IPG(12M)), ADC High Speed Configuration(ADHSC) isn't enabled and ADC1/2 clock gates are enabled, no any improvement. Is ADC able to work in low power run mode? If so, what else I can try? Thank you!

Case 1, use default settings (ADACK clock), it works in full speed run mode, but not low power run mode.

ADC_GetDefaultConfig(&adcConfigStrcut);

ADC_Init(ADC_BASE, &adcConfigStrcut);

Case 2, use 12MHz IPG clock, only tried in low power run mode, it doesn't work.

ADC_GetDefaultConfig(&adcConfigStrcut);

adcConfigStrcut.enableAsynchronousClockOutput = false;

adcConfigStrcut.clockSource = kADC_ClockSourceIPG;

ADC_Init(ADC_BASE, &adcConfigStrcut);

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tom,

There should not be an issue with that. As you can see in the application note I mentioned, Low Power Bandgap is disabled only in SNVS mode and Normal Bandgap is disabled in Low Power Idle, Suspend and SNVS mode.

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi nxf46115

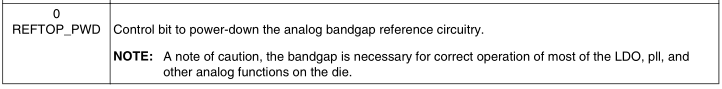

I found the cause. While entering low power run code, the analog bandgap reference circuitry would be powered down by setting bit REFTOP_PWD.

See SDK code LPM_LowPowerRun()->BandgapOff(). Can I keep this bit 0 and ADC available in low power run mode? Noticing the message below, I concern the power mode switching issues if a wrong setting of bit here, my system needs MCU to work in full speed run and low power run mode. Do you have any suggestion of making ADC usable in both low power run and full speed run modes?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tom,

There should not be an issue with that. As you can see in the application note I mentioned, Low Power Bandgap is disabled only in SNVS mode and Normal Bandgap is disabled in Low Power Idle, Suspend and SNVS mode.

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks nxf46115!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Tom,

I recommend you to check How to use i.MX RT Low Power Feature application note. In Low power run mode, all PLL are powered down.

If you use IPG CLK ADC should be able to work in Low Power run mode, please make sure you enable low power configuration in ADC_CFG[ADLPC] register.

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Felipe,

Thank you for looking at it.

The low power run mode has been working fine, the problem is only that ADC failed to work in this mode. By enabling ADLPC, still no any improvement, ADCx_GS is the same as before, reporting CALF(Calibration Failed Flag), but the hardware trigger isn't selected, no any ADC register setting, and stop mode has never been entered. The internal clock of ADC (ADACK) is dedicated whatever is in full speed run mode or low power run mode, I don't understand why the same ADC settings (or add ADLPC) doesn't work in low power run mode. By the way, its long sample mode (ADLSMP) was tried, not working either.