- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- DMA error in Channel 81

DMA error in Channel 81

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everyone,

I'm using DMA to perform readings from ADC_ETC, and it's working correctly.

So far, I've been using a PWM trigger to start the conversion, and at the end of the ADC_ETC chain, it generates a DMA request on channel 64: ADC_ETC.

Now, I want to use 2 PWM triggers to perform two different chains and have them generate two DMA requests on two different channels.

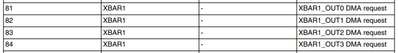

As a first step, I've linked COCO0 to DMA channel 81 using XBAR, and in DMA0, I simply modified the transfer channel from 64 to 81. However, this didn't work.

While debugging (by routing COCO0 to a pin), I've noticed that a 40ms pulse is generated correctly, leading me to believe that the issue lies within the DMA. What could be happening? Even when generating pulses manually on DMA channel 81, no transfer is performed.

Best regards,

iMXRT1170

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @oayastuy,

Could you please try using the RT1170 EVKB SDK's xbara_cm7 example to use channel 81? The example uses kXBARA1_OutputDmaChMuxReq81 with PIT interruption, but could be useful to see how the channel 81 is being configured.

Also, if possible, could you please share your XBARA configuration for further analysis?

Best regards, Raul.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @oayastuy,

Just for double check, could you please verify you are linking COCO0 to XBAR1_OUT0 as DMA request on channel 81 responds to XBAR1_OUT0?

[i.MX RT1170 Processor Reference Manual. Chapter 4. Interrupts, DMA Events, and XBAR Assignments. Table 4-3. DMA Mux Mapping]

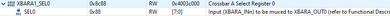

On RT1170 for configure the XBAR1_OUT0 please refer to i.MX RT1170 Processor Reference Manual. Chapter 83. Inter-Peripheral Crossbar Switch A (XBARA). There, could you please verify your configuration of XBARAx_SEL0 and XBARAx_CTRL0 registers?

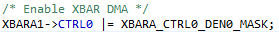

XBARAx_CTRL0 register needs to be configured to enable the DMA for XBAR_OUT0 in bit 0 [DEN0].

Best regards, Raul.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raul,

I checked what you say with the following results:

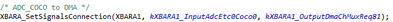

- COCO0 is linked to XBAR1_OUT0

- Code:

- XBARAx_SEL0 Register value

:

- Code:

- DMA is enabled for OUT0:

- Code:

- XBARAx_CTRL0 registers DEN0 bit value:

- Code:

Still, even though it works with the ADC_ETC channel (channel 64), I can't get it to work with the XBAR1_OUT00 channel (channel 81).

Best regards, Odei.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @oayastuy,

Could you please try using the RT1170 EVKB SDK's xbara_cm7 example to use channel 81? The example uses kXBARA1_OutputDmaChMuxReq81 with PIT interruption, but could be useful to see how the channel 81 is being configured.

Also, if possible, could you please share your XBARA configuration for further analysis?

Best regards, Raul.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Raul,

Thank you for your response. I have successfully resolved the problem by following the provided example.

The resulting code is as follows:

/* Init xbara module. */

XBARA_Init(XBARA1);

/* Link the ADC_ETC trigger signals from PWM*/

XBARA_SetSignalsConnection(XBARA1, kXBARA1_InputFlexpwm1Pwm0OutTrig0, kXBARA1_OutputAdcEtc0Coco0);

XBARA_SetSignalsConnection(XBARA1, kXBARA1_InputFlexpwm1Pwm0OutTrig1, kXBARA1_OutputAdcEtc0Coco1);

/* Link the ADC_COCO signal to DMA */

XBARA_SetSignalsConnection(XBARA1, kXBARA1_InputAdcEtc0Coco0, kXBARA1_OutputDmaChMuxReq81);

XBARA_SetSignalsConnection(XBARA1, kXBARA1_InputAdcEtc1Coco0, kXBARA1_OutputDmaChMuxReq82);

/* Configure the XBARA DMA. */

xbaraConfig1.activeEdge = kXBARA_EdgeRising;

xbaraConfig1.requestType = kXBARA_RequestDMAEnable;

XBARA_SetOutputSignalConfig(XBARA1, kXBARA1_OutputDmaChMuxReq81, &xbaraConfig1);

xbaraConfig2.activeEdge = kXBARA_EdgeRising;

xbaraConfig2.requestType = kXBARA_RequestDMAEnable;

XBARA_SetOutputSignalConfig(XBARA1, kXBARA1_OutputDmaChMuxReq82, &xbaraConfig2);

Best regards,

Odei