- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- iMX8M plus - M7 trigger watchdog and A53 halt

iMX8M plus - M7 trigger watchdog and A53 halt

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMX8M plus - M7 trigger watchdog and A53 halt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NXP,

There are A53 and M7 in iMX8M plus EVK and I wish I can establish a data link between A53 and M7 to keep them sync data (maybe just simple echo or ping-pong). Once the data sync is missing over timeout time, I can make M7 trigger watchdog to reset A53 and itself.

I download M7 SDK from https://mcuxpresso.nxp.com/en/select and verify the watchdog example.

There are some problems:

1. M7 can trigger watchdog to reset itself, but A53 halt when M7 trigger watchdog

2. Once A53 halt, M7 trigger watchdog again, and M7 halt

3. M7 can not free run. There's no debug message output by M7.

To test and verify:

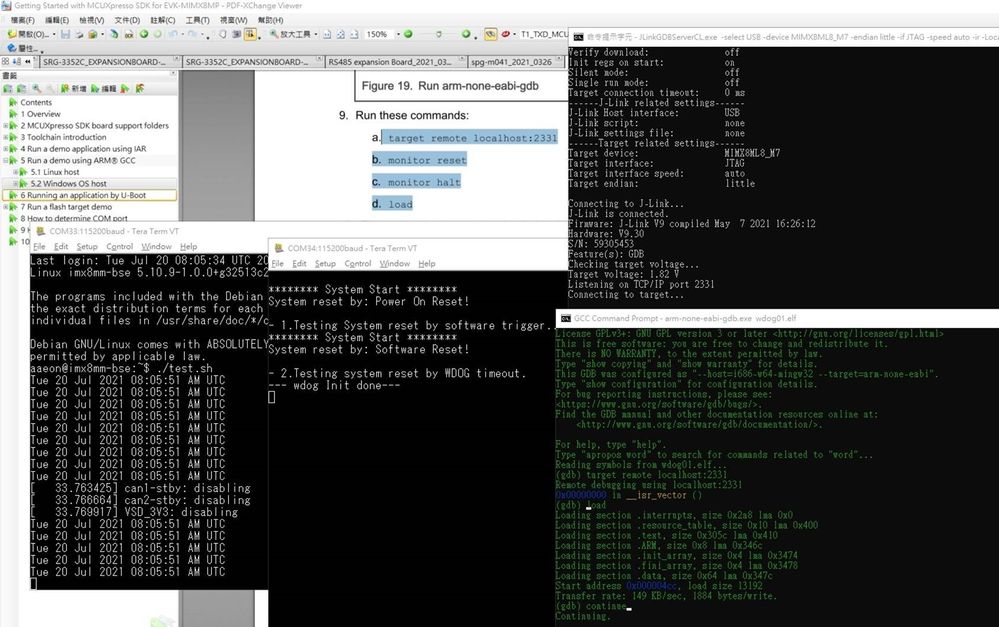

M7: wdog example (SDK_2_10_0_EVK-MIMX8MP\boards\evkmimx8mp\driver_examples\wdog)

A53: run a simple script to show the date and time every two seconds to confirm if it is working

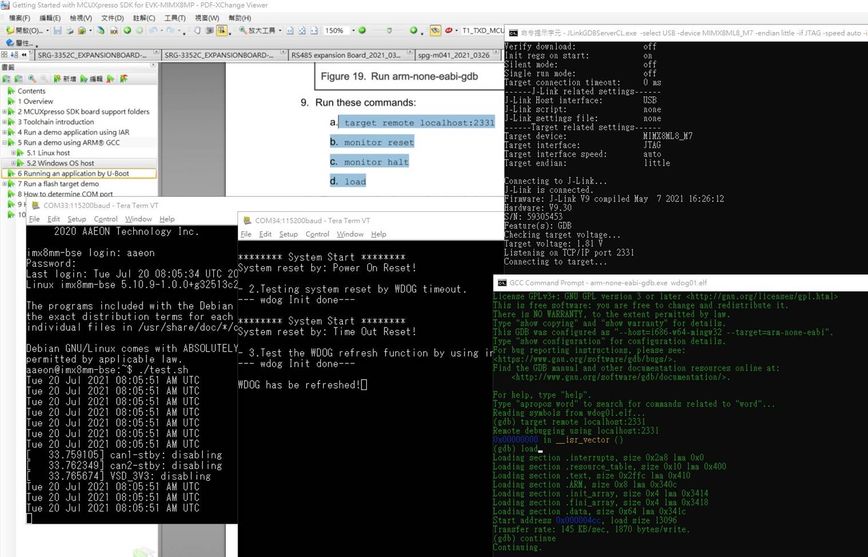

1. M7 can trigger the first watchdog to reset itself, but A53 halt when M7 triggered the first watchdog.

Then M7 triggers the second watchdog and halt.

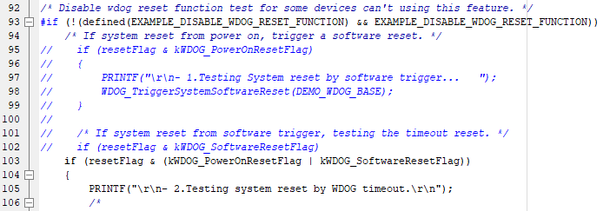

2. Modify watchdog example to ignore the first trigger software reset testing.

No matter it starts from power on reset or software reset, it will run watchdog timeout reset testing

When M7 watchdog timeout and trigger reset, A53 still halt

3. Remove segger j-link debugger, turn off power and turn on to let M7 free run.

There's no debug message output from M7.

I test hello_world example (\SDK_2_10_0_EVK-MIMX8MP\boards\evkmimx8mp\demo_apps\hello_world), and there's no debug message output either.

I also download and debug by IAR and it is OK, but there's no debug message output when free run either.

Sophie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

M7 can trigger watchdog to reset itself, but A53 halt when M7 trigger watchdog

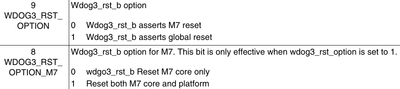

I'm hitting the same issue on imx8mp evk (MIMX8ML8), even though WDOG3_RST_OPTION and WDOT3_RST_OPTION_M7 of SRC_M7RCR (3039_000C) have been set to 0. We need the wdog to reset the M core only. Please note that this works on imx8mm evk (MIMX8MM6).

I have tried all 4 combinations of 00,01,10,11, none of them fixes the issue.

Could anyone provide some advice?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

BTW, about question3, how to make M7 free run? (without j-link debugger)

I cannot make M7 do anything if it can not free run.

Sophie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

In IMX8MPRM.pdf (i.MX 8M Plus Applications Processor Reference Manual)

Chapter 6.6 Watchdog Timer (WDOG)

I don't quite understand this description.

Will A53 custom timeout watchdog trigger WDOG_B to reset pmic to reset both A53 and M7?

User can custom watchdog timer 0.5 ~ 128 secs, which will trigger WDOG_RESET_B_DEB.

What happen when WDOG_RESET_B_DEB triggered?

What reset fixed 16 secs power down counter to prevent it trigger WDOG_B to reset pmic?

Can M7 trigger WDOG_B, too?

If yes, M7 can do what I want it to do.

Besides, is this resetting flow correct?

M7 watchdog timeout -> A53 halt -> A53 watchdog timeout -> reset pmic -> reset both A53 and M7.

Sophie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

>Will A53 custom timeout watchdog trigger WDOG_B to reset pmic to reset both A53 and M7?

yes, please look at first answer.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can M7 trigger WDOG_B, too?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sophie

I am afraid such A53 reset is not supported in BSPs, supported case with signal

WDOG_B (CPU WDOG_B Reset) on i.MX8M PLus LPDDR4 EVK schematic, SPF-46368 p.11

resetting pmic PCA9450CHN (U6C).

Best regards

igor