- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

iMX6UL WDOG1 external signal

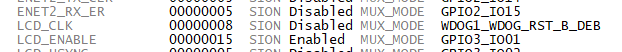

We are setting up the iMX internal watchdog at the moment. On our board we have routed the LCD_CLK (WDOG1_RST_B_DEB) to our reset circuitry. We have it activated in the device tree

The pin is configured correctly (can be seen by debugger) as WDOG1_RST_B_DEB.

But, when executing echo b >/proc/sysrq-trigger for example, the board just hangs up and doesnt assert the RST_B_DEB pin low. Neither a hardware or a software reset happens. It seems like we broke the reset chain somehow by routing the RST_B_DEB to external.

Could you see any problem with that? Or do we have to use the LCD_RESET multiplex WDOG1_ANY

Hi Philipp

one can check signal with oscilloscope and debug if necessary in driver

function imx2_wdt_restart(), ext_reset :

imx2_wdt.c\watchdog\drivers - linux-imx - i.MX Linux kernel

To avoid hanging it is necessary to remove shortly all power from board

as it is done on i.MX6UL EVK schematic SPF-2861 p.10 U708

Design files, including hardware schematics, Gerbers, and OrCAD files

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Good morning Igor,

thanks for your quick reply!

As I can see from the imx2_wdt_restart() function, internal and external reset simultaneously is not possible. Understood. Our design features a reset chip, just like the EVK (STM6679Y).

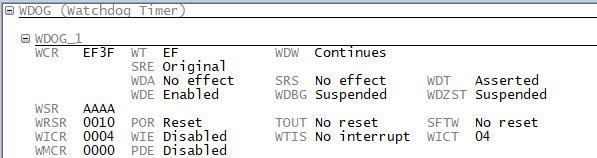

The problem is that the wdog1_rst_b_deb is not getting asserted. It is configured as such, but doesn't react. Please find the configuration after bootup below:

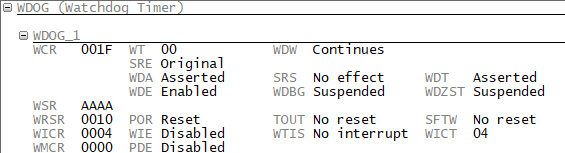

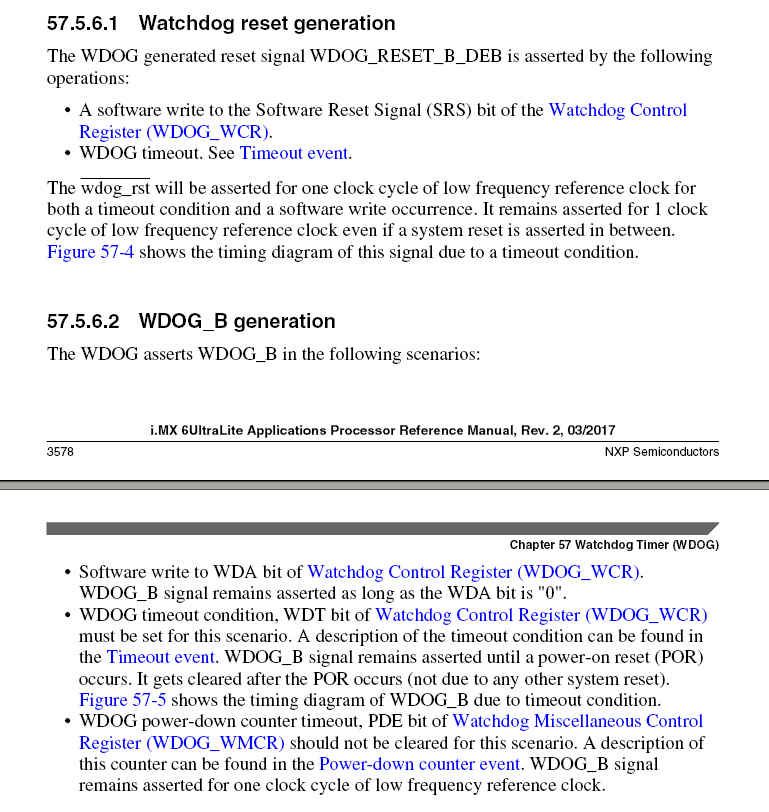

Here is the watchdog register after sending a "echo b >/proc/sysrq-trigger" to trigger the watchdog, the system hangs up at this point because no external reset takes place. The wdog1_rst_b_deb external pin remains logical HIGH.

Can you please give an advice what prevents the pin from getting asserted?

Another problem is that the processor seems to loose informations about the reset cause, it displays POR on following startup, not WDOG. For sure it looses this information because of the power cycle. Do you have a solution for that?

Hi Philipp

>Can you please give an advice what prevents the pin from getting asserted?

suggest to attach jtag and test behavior setting bit with debugger and observing signal with oscilloscope.

>Another problem is that the processor seems to loose informations about the reset cause, it displays POR on following >startup, not WDOG. For sure it looses this information because of the power cycle. Do you have a solution for that?

your understanding is correct, unfortunatlely there is no solution for that.

Best regards

igor

Hi Igor,

which bit are you exactly talking about? When setting SRS bit, it doesn't matter if wdog_rst_b_deb is configured as such or not, the pin will fall low (due to internal driver shutdown). It doesn't get asserted intentionally. WDA bit is set on watchdog triggering but the wdog_rst_b_deb bin remains high

Kind regards,

Philipp

Hi Philipp

>which bit are you exactly talking about?

Best regards

igor