i.MX8MQ LPDDR4 RPA register configuration

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I am now trying to get the LPDDR4 on customized board with i.mx8mq to work but face some problem.

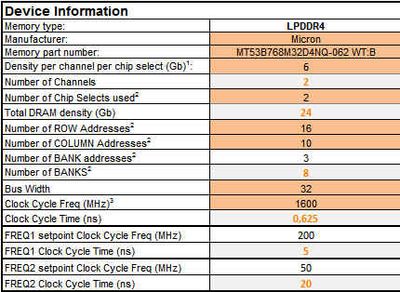

The configuration is generated by the MX8M_LPDDR4_RPA_v29.

There's a question towards all the DFI clock related registers in the RPA, for example, the PRE_CKE_X1024 in DDRC_INIT0.

In the programming aid, the PRE_CKE_X1024 calculation formula: LPDDR4: tINIT3 of 2 ms (min)

When the controller is operating in 1:2 frequency ratio mode, program this to JEDEC spec value divided by 2, and round it up to the next integer value.

Then the PRE_CKE_X1024 should be calcluated as: 2ms/2 = 1ms (since the controller is operating in 1:2 frequency ratio mode).

If my understanding is correct, for DDR frequency 1600MHz(3200MTS), the DFI frequency should be 800MHz.

And the PRE_CKE_X1024 is in the unit of 1024 DFI clock, which is 1024/(800*10^3) ms, so 1ms should be around 781 of 1024 DFI clocks.

But in the RPA, the configuration is set to 1564.

Please help if there's any misunderstanding.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jay

for frequencies it is necessary to fill parameters as below, all other parameters

are calculated automatically

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for your reply.

But my question is not answered