- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello NXP,

We have designed a board based on the i.MX8M mini reference design.

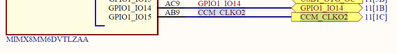

Our customer would like to output a clock of 24MHz on CCM_CLK02 pad AB9 of the chip

- What is the configuration needed to be done in the dts or any other relevant code to output the 24MHz?

- Is it possible to output this clock @24MHz in Linux only or in both u-boot and Linux?

Best regards!

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No matter which version of bsp, you can modify the clock driver manually. However, do not copy these codes directly. Because each version will be different.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No matter which version of bsp, you can modify the clock driver manually. However, do not copy these codes directly. Because each version will be different.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Try below, please!

--------------------------------

diff --git a/drivers/clk/imx/clk-imx8mm.c b/drivers/clk/imx/clk-imx8mm.c

index 5709bfce578c..2ef53f153728 100644

--- a/drivers/clk/imx/clk-imx8mm.c

+++ b/drivers/clk/imx/clk-imx8mm.c

@@ -404,6 +404,9 @@ static struct clk ** const uart_clks[] __initconst = {

static const char *imx8mm_clko1_sels[] = {"osc_24m", "sys_pll1_800m", "osc_27m", "sys_pll1_200m", "audio_pll2_clk",

"vpu_pll", "sys_pll1_80m", };

+static const char *imx8mm_clko2_sels[] = {"osc_24m", "sys_pll2_200m", "sys_pll1_400m", "sys_pll2_166m", "sys_pll3_out",

+ "audio_pll1_clk", "vpu_pll_out", "osc_32k", };

+

static int __init imx_clk_init_on(struct device_node *np,

struct clk * const clks[])

{

@@ -665,6 +668,7 @@ static void __init imx8mm_clocks_init(struct device_node *ccm_node)

clks[IMX8MM_CLK_WDOG_SRC] = imx_clk_mux2("wdog_src", base + 0xb900, 24, 3, imx8mm_wdog_sels, ARRAY_SIZE(imx8mm_wdog_sels));

clks[IMX8MM_CLK_WRCLK_SRC] = imx_clk_mux2("wrclk_src", base + 0xb980, 24, 3, imx8mm_wrclk_sels, ARRAY_SIZE(imx8mm_wrclk_sels));

clks[IMX8MM_CLK_CLKO1_SRC] = imx_clk_mux2("clko1_src", base + 0xba00, 24, 3, imx8mm_clko1_sels, ARRAY_SIZE(imx8mm_clko1_sels));

+ clks[IMX8MM_CLK_CLKO2_SRC] = imx_clk_mux2("clko2_src", base + 0xba80, 24, 3, imx8mm_clko2_sels, ARRAY_SIZE(imx8mm_clko2_sels));

clks[IMX8MM_CLK_DSI_CORE_SRC] = imx_clk_mux2("dsi_core_src", base + 0xbb00, 24, 3, imx8mm_dsi_core_sels, ARRAY_SIZE(imx8mm_dsi_core_sels));

clks[IMX8MM_CLK_DSI_PHY_REF_SRC] = imx_clk_mux2("dsi_phy_ref_src", base + 0xbb80, 24, 3, imx8mm_dsi_phy_sels, ARRAY_SIZE(imx8mm_dsi_phy_sels));

clks[IMX8MM_CLK_DSI_DBI_SRC] = imx_clk_mux2("dsi_dbi_src", base + 0xbc00, 24, 3, imx8mm_dsi_dbi_sels, ARRAY_SIZE(imx8mm_dsi_dbi_sels));

diff --git a/include/dt-bindings/clock/imx8mm-clock.h b/include/dt-bindings/clock/imx8mm-clock.h

index 083dd6d0116d..0745122611ca 100644

--- a/include/dt-bindings/clock/imx8mm-clock.h

+++ b/include/dt-bindings/clock/imx8mm-clock.h

@@ -469,5 +469,7 @@

#define IMX8MM_CLK_NAND_USDHC_BUS_RAWNAND_CLK 455

#define IMX8MM_CLK_SIM_HSIO 456

-#define IMX8MM_CLK_END 457

+#define IMX8MM_CLK_CLKO2_SRC 457

+

+#define IMX8MM_CLK_END 458

#endif

--

-----------------------------------------------

Hope it is helpful to you.

Have a nice day!

B.R,

Weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Sun for your reply!

- Can you please tell me what kernel version is the diff generated from?

- Do you have a more recent patch based on kernel 5.4.24?

Best regards.