- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Queries on iMX6 Solo processor : DDR3L Differentail clock,Video Decoder signals, PMIC F6 variant sequence

Queries on iMX6 Solo processor : DDR3L Differentail clock,Video Decoder signals, PMIC F6 variant sequence

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Queries on iMX6 Solo processor : DDR3L Differentail clock,Video Decoder signals, PMIC F6 variant sequence

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

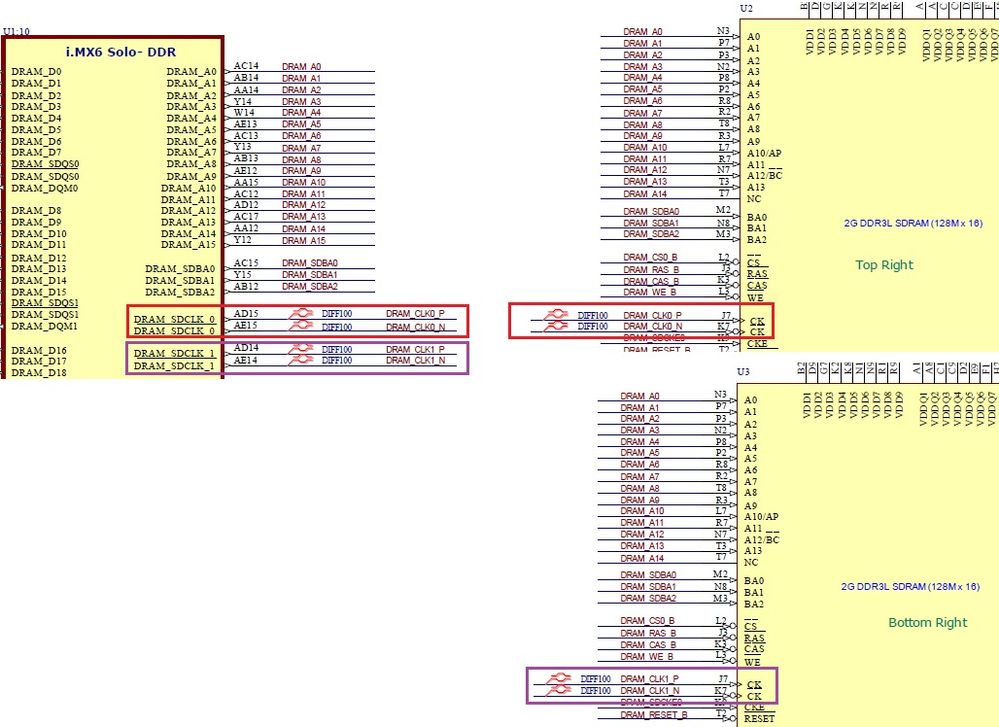

- We are using 2-chip solution of 2G DDR3L SDRAM (128M x 16) memory. we are connecting DRAM_SDCLK_0 (P/N) from processorto first device (U2) of DRR3L CLK (P/N) and DRAM_SDCLK_1 (P/N) from processor to second device (U3) of DRR3L CLK (P/N).

Is it correct ? (OR) Do we need to use any one DRAM_SDCLK from processor to DDR3L chips for 32 Bit configuration? Please see attachment Q1 snap-shot RED and Purple colour used to differentiate the Signals and connection in our schematic.

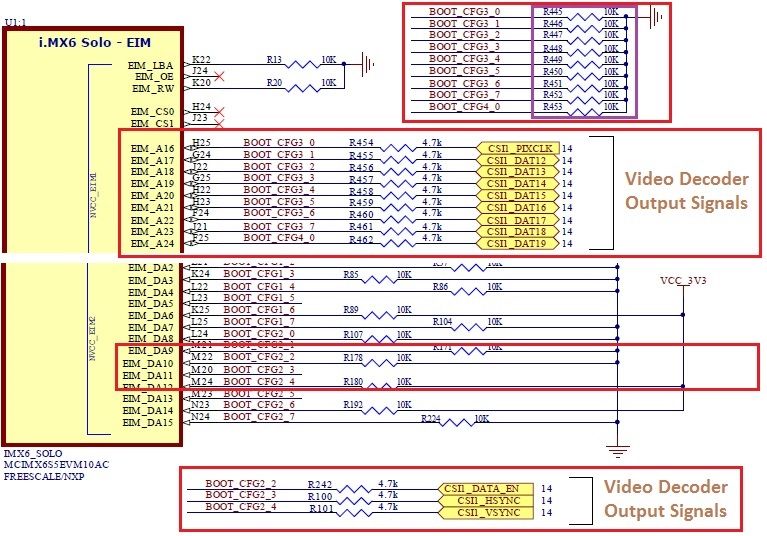

- We are connecting Video Decoder Output signals to "EIM_A16 to EIM_A24" & "EIM_DA10 to EIM_DA12" pins of SOC (i.MX6Solo). These SOC pins are used for Boot Configuration 3 & 4 and connected to ground through 10K ohm for proper Booting sequence, after booting these pins we used for CSI1 interface (ALT2).Is these 10K ohm pull down resistors will degrade our Video Decoder signal processing ?

Please see attachment Q2 snap-shot RED & purple coloured. - We used PMIC part number (MMPF0100F6AEP) based on its Default output of the switching regulator "SW3A & SW3B" is 1.35V which we were using for DDR3L . But this part number Power up sequence has slight difference from the earlier Part number (MMPF0100F0EP) which was used in SABRESD Flatform. VGEN6 (3.0V) O/P will be Sequence - 1 used for VDDHIGH_IN power pin of SOC & SW1AB (1.375 V), SW1C (1.375 V) O/P will be Sequence - 2 used for VDDCORE ,VDDSOC power pin of SOC. Is this sequence will cause any problem?

Thanks in Advance for your support.

Thanks & Regards,

Rameshkumar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ramesh

-DRAM_SDCLK_0 ,1 connections are correct (these pads outputs identical clock).

-you are right, 10K ohm pull down resistors will change signal, however

one can increase drive strength of these signals and use ibis modelling

if necessary.

-MMPF0100F6AEP sequence will not cause problems.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Igor,

Thanks for your quick response its very helpful.

I would like to discuss our Software team about IBIS modelling and plan for External Hardware IO-buffers if its really require. Any further more queries we will get back to you soon.

Thanks & Regards,

Rameshkumar