- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: IS25LP032D flash settings

IS25LP032D flash settings

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IS25LP032D flash settings

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Custom RT1052 board. We are failing to commit our program over jtag. Log below.

Does someone have the flash settings for the ‘IS25LP032D’ ? I don’t see a built in driver for this.

Thanks.

Mark

Executing flash operation 'Program' (Program executable into flash evkbimxrt1050_hello_world.axf) - Wed Dec 07 16:31:40 EST 2022

Checking MCU info...

Scanning for targets...

Executing flash action...

SEGGER J-Link Commander V7.70d (Compiled Aug 30 2022 17:10:56)

DLL version V7.70d, compiled Aug 30 2022 17:10:47

J-Link Command File read successfully.

Processing script file...

J-Link>ExitOnError 1

J-Link Commander will now exit on Error

J-Link>r

J-Link connection not established yet but required for command.

Connecting to J-Link via USB...O.K.

Firmware: J-Link Pro V5 compiled Aug 30 2022 11:48:23

Hardware version: V5.00

J-Link uptime (since boot): 0d 00h 23m 23s

S/N: 175000067

License(s): RDI, FlashBP, FlashDL, JFlash, GDB

USB speed mode: High speed (480 MBit/s)

IP-Addr: DHCP (no addr. received yet)

VTref=3.335V

Target connection not established yet but required for command.

Device "MIMXRT1052XXXXA" selected.

Connecting to target via SWD

Found SW-DP with ID 0x0BD11477

DPIDR: 0x0BD11477

CoreSight SoC-400 or earlier

Scanning AP map to find all available APs

AP[1]: Stopped AP scan as end of AP map has been reached

AP[0]: AHB-AP (IDR: 0x04770041)

Iterating through AP map to find AHB-AP to use

AP[0]: Core found

AP[0]: AHB-AP ROM base: 0xE00FD000

CPUID register: 0x411FC271. Implementer code: 0x41 (ARM)

Found Cortex-M7 r1p1, Little endian.

FPUnit: 8 code (BP) slots and 0 literal slots

CoreSight components:

ROMTbl[0] @ E00FD000

[0][0]: E00FE000 CID B105100D PID 000BB4C8 ROM Table

ROMTbl[1] @ E00FE000

[1][0]: E00FF000 CID B105100D PID 000BB4C7 ROM Table

ROMTbl[2] @ E00FF000

[2][0]: E000E000 CID B105E00D PID 000BB00C SCS-M7

[2][1]: E0001000 CID B105E00D PID 000BB002 DWT

[2][2]: E0002000 CID B105E00D PID 000BB00E FPB-M7

[2][3]: E0000000 CID B105E00D PID 000BB001 ITM

[1][1]: E0041000 CID B105900D PID 001BB975 ETM-M7

[1][2]: E0042000 CID B105900D PID 004BB906 CTI

[0][1]: E0040000 CID B105900D PID 000BB9A9 TPIU-M7

[0][2]: E0043000 CID B105F00D PID 001BB101 TSG

Cache: Separate I- and D-cache.

I-Cache L1: 32 KB, 512 Sets, 32 Bytes/Line, 2-Way

D-Cache L1: 32 KB, 256 Sets, 32 Bytes/Line, 4-Way

Cortex-M7 identified.

Reset delay: 0 ms

Reset type NORMAL: Resets core & peripherals via SYSRESETREQ & VECTRESET bit.

ResetTarget() start

Core did not halt on flash image verification. Assuming faulty flash settings.

Halting target manually.

ResetTarget() end

AfterResetTarget() start

AfterResetTarget() end

J-Link>h

PC = 0020C74A, CycleCnt = 00000000

R0 = 402E0000, R1 = 00000080, R2 = 00000001, R3 = 00000000

R4 = 202069E0, R5 = 00000000, R6 = 00000047, R7 = 00000010

R8 = 401F4470, R9 = 20203A00, R10= 0BD0C057, R11= 00000000

R12= 00000004

SP(R13)= 20200F78, MSP= 20200F78, PSP= 00000000, R14(LR) = 0020D137

XPSR = 61000000: APSR = nZCvq, EPSR = 01000000, IPSR = 000 (NoException)

CFBP = 00000000, CONTROL = 00, FAULTMASK = 00, BASEPRI = 00, PRIMASK = 00

FPS0 = 00000000, FPS1 = 00000000, FPS2 = 00000000, FPS3 = 00000000

FPS4 = 00000000, FPS5 = 00000000, FPS6 = 00000000, FPS7 = 00000000

FPS8 = 00000000, FPS9 = 00000000, FPS10= 00000000, FPS11= 00000000

FPS12= 00000000, FPS13= 00000000, FPS14= 00000000, FPS15= FFFFFFFF

FPS16= 00000000, FPS17= 00000000, FPS18= 00000000, FPS19= 00000000

FPS20= 00000000, FPS21= 00000000, FPS22= 00000000, FPS23= 00000000

FPS24= 00000000, FPS25= 00000000, FPS26= 00000000, FPS27= 00000000

FPS28= 00000000, FPS29= 00000000, FPS30= 00000000, FPS31= FFFFFFFF

FPSCR= 00000000

J-Link>loadfile "/Users/mrecoskie/Documents/MCUXpressoIDE_11.6.1_8255/workspace/evkbimxrt1050_hello_world/Debug/evkbimxrt1050_hello_world.hex"

'loadfile': Performing implicit reset & halt of MCU.

ResetTarget() start

Core did not halt on flash image verification. Assuming faulty flash settings.

Halting target manually.

ResetTarget() end

AfterResetTarget() start

AfterResetTarget() end

Downloading file [/Users/mrecoskie/Documents/MCUXpressoIDE_11.6.1_8255/workspace/evkbimxrt1050_hello_world/Debug/evkbimxrt1050_hello_world.hex]...

****** Error: Timeout while preparing target, core does not stop. (PC = 0x2000017A, XPSR = 0x41000000, SP = 0x20000B18)!

Failed to perform RAMCode-sided Prepare()

Unspecified error -1

Script processing completed.

Unable to perform operation!

Command failed with exit code 1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can try this jlink flashloader (RT-UFL) for IS25LP032D, default jlink flashloader of RT1052 is for HyperFlash

RT-UFL - 一个适用全平台i.MXRT的超级下载算法设计

超级下载算法RT-UFL v1.0发布,附J-Link下安装教程

超级下载算法RT-UFL v1.0在MCUXpresso IDE下的使用

超级下载算法RT-UFL v1.0在IAR EW for Arm下的使用

超级下载算法RT-UFL v1.0在Keil MDK下的使用

超级下载算法RT-UFL v1.0在Segger Ozone下的使用

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

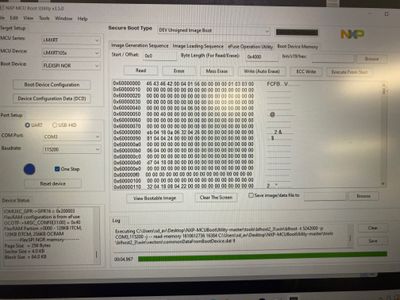

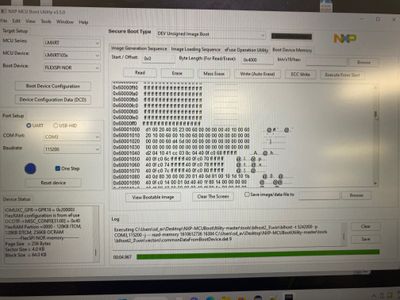

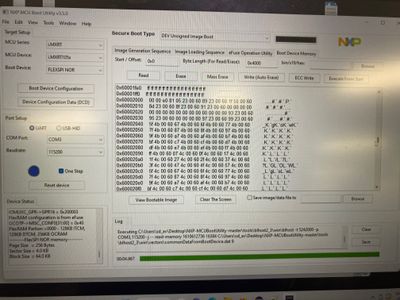

We have tried using the slightly older NXP-MCUBootUtility. With the flash settings for the ISSI_IS25LPxxxA it seems to read the flash successfully over the UART and through the serial flash loader. I imagine this confirms the FlexSPI bus and flash design. Now how to make this work for our program?

Below are the program defines and qspiflash_config in the MCUxpresso IDE produced software. A simple 'hello_world' program via UART is used. When we boot we get no UART output.

const flexspi_nor_config_t qspiflash_config = {

.memConfig =

{

.tag = FLEXSPI_CFG_BLK_TAG,

.version = FLEXSPI_CFG_BLK_VERSION,

.readSampleClksrc=kFlexSPIReadSampleClk_LoopbackFromDqsPad,

.csHoldTime = 3u,

.csSetupTime = 3u,

.sflashPadType = kSerialFlash_4Pads,

.serialClkFreq = kFlexSpiSerialClk_100MHz,

.sflashA1Size = 4u * 1024u * 1024u,

.lookupTable =

{

// 0 Read LUTs

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0xEB, RADDR_SDR, FLEXSPI_4PAD, 0x18),

FLEXSPI_LUT_SEQ(DUMMY_SDR, FLEXSPI_4PAD, 0x06, READ_SDR, FLEXSPI_4PAD, 0x04),

0,0,

// 1 Read Status

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x81, READ_SDR, FLEXSPI_1PAD, 0x04),

0,0,0,

// 2 Reserved

0,0,0,0,

// 3 Write Enable

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x06, STOP, FLEXSPI_1PAD, 0),

0,0,0,

// 4 Reserved

0,0,0,0,

// 5 Erase Sector

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0xD7, RADDR_SDR, FLEXSPI_1PAD, 0x18),

0,0,0,

// 6 Reserved

0,0,0,0,

// 7 Reserved

0,0,0,0,

// 8 Reserved

0,0,0,0,

// 9 Page Program

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0x32, RADDR_SDR, FLEXSPI_1PAD, 0x18),

FLEXSPI_LUT_SEQ(WRITE_SDR, FLEXSPI_4PAD, 0x04, STOP, FLEXSPI_1PAD, 0),

0,0,

// 10 Reserved

0,0,0,0,

// 11 Chip Erase

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0xC7, STOP, FLEXSPI_1PAD, 0),

0,0,0,

// 12 Reserved

0,0,0,0,

},

},

.pageSize = 256u,

.sectorSize = 4u * 1024u,

.blockSize = 64u * 1024u,

.isUniformBlockSize = false,

};

Perhaps you can suggest what to check next? Thanks.

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your qspiflash_config header is ok for IS25LP032D.

When you flash this image by MCUBootUtility, then you switch boot_mode to 2'b10 and re-power up the board, does it boot properly?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

No. It doesn't fully boot up.

Unfortunately I don't have JTAG access to find out how far it gets.

Thanks,

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Different tools like the MCUBootUtility and the Secure Provisioning tool have different abilities to write the FDCB and IVT and Application.

Could someone suggest one image and one method which is known to work with the RT1052 and IS25LP032D flash connected via FlexSPIA?

Or perhaps the memory contents could be spot checked?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Looking at the flash memory through MCU-BootUtility tool everything looks correct to me except the 'Absolute address of the first instruction to execute from the image' offset 0x04-0x07 at 0x1000 in the IVT. (as per AN12107) But from my understand the IVT is written by the tool - how could this be incorrect?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Because of the flash size difference (32 vs 64) is it possible the built in driver 'MIMXRT1050-EVK_IS25WP064A.cfx' needs to be updated as per this reference -

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mrecoskie ,

To MCUBootUtility, form SDKv2.10.0, Reset_Handler() is used as entry point, not vector table. So, it seems the 0x60002035 is correct.(base on your image) MCUBootUtility will replace your FDCB by default. If it can read/write flash already, the auto generated FDCB should be correct.

To jlink flash algorithm, I think the better way is to follow Jay's suggestion, using RT-UFL can make it simple. You needn't make a new .cfx. The reference link shows how to make a .cfx for RT1052. RT1020 can't use it. At least you should modify the pin config. You can start from the iMXRT1050_QSPI.zip.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Jing. Is there any additional documentation on RT-UFL?

For example, what operating systems are supported and how to build and run the application?

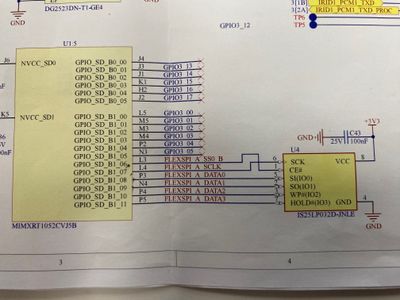

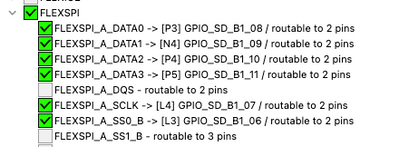

Below is the schematic of the processor / memory connection as well as the pin definitions.

Is it possible the QE bit on the flash needs to be enabled? If so, what is the easiest way to do this?

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mrecoskie ,

RT-UFL support Keil/IAR/MCUXpresso. There is only Chinese document.

https://www.cnblogs.com/henjay724/p/13951686.html

https://www.cnblogs.com/henjay724/p/15430619.html

https://www.cnblogs.com/henjay724/p/14942574.html

The MCUBootUtility will program QE bit at first time programming. When massive product, you can make a special application to program QE bit.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks. I am wondering if the size difference of 32 vs 64 is somehow a factor here.

From SWD trace the processor seems to be getting stuck in the Boot ROM. Is there any way to get more information into what is happening? A piece of the log is below:

2000036a: lsls r5, r5, #19

2000036c: bkpt 0x00b4

2000036e: movs r5, #162 ; 0xa2

20000370: cmp r7, r4

20000372: ldc2l 10, cr11, [r10, #52]! ; 0x34 ; <UNPREDICTABLE>

20000376: subs r1, #73 ; 0x49

20000378: ldmia.w r9, {r1, r2, r4, r6, r7, r9, r11, r12, pc}

2000037c: add r5, sp, #976 ; 0x3d0

2000037e: dvfsp f4, f6, #1.0

......... ...

deadbcae: Failed to execute MI command:

-data-disassemble -s 3735927982 -e 3735928174 -- 3

Error message from debugger back end:

Cannot access memory at address 0xdeadbcae

deadbcaf: Failed to execute MI command:

-data-disassemble -s 3735927982 -e 3735928174 -- 3

Error message from debugger back end:

Cannot access memory at address 0xdeadbcae

deadbcb0: Failed to execute MI command:

-data-disassemble -s 3735927984 -e 3735928174 -- 3

Error message from debugger back end:

Cannot access memory at address 0xdeadbcb0

(Normally there is a jump onto the flash at 0x60000000)

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mrecoskie ,

Can you share your application and binary image? (include FDCB/IVT/DCD)

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The application is the hello_world sample with four modifications.

1) I've tried both the 'MIMXRT_1050_SFDP_QSPI.cfx' and 'MIMXRT_1050_IS25WP064A.cfx' Driver settings under the Project Settings > Memory.

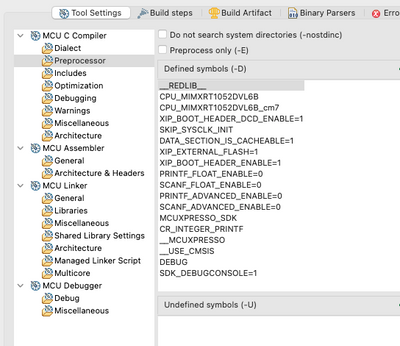

2) I've set the preprocessor defines 'XIP_BOOT_HEADER_ENABLE=1', 'XIP_EXTERNAL_FLASH=1' and 'XIP_BOOT_HEADER_DCD_ENABLE=1'.

3) I've defined a 'flexspi_nor_config_t qspiflash_config' in the 'evkbimxrt1050_flexspi_nor_config.c' as found above in this thread.

4) I've made pin route definitions for the FlexSPIA bus, UART, JTAG and SRC pins.

These are the only changes. Please find attached.

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mrecoskie ,

Segger JLINK is very special. It doesn't use RT1050_SFDP_QSPI.cfx or RT1050_EVK_IS25WP064.cfx assigned by MCUXpresso. This is way we suggest you to use RT-UFL.

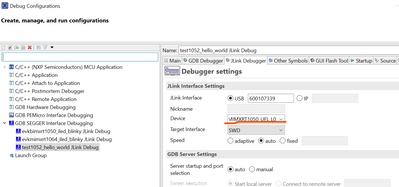

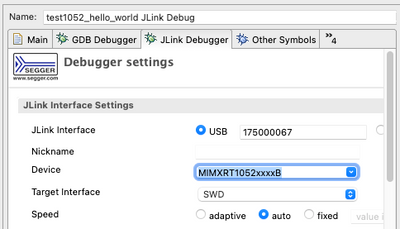

After you install RT-UFL, you should assign program algorithm here.

I tested your project, it can debug in mcuxpresso.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks. How do you install RT-UFL?

I try importing the 'iMXRT1050_QSPI' project in the MCUxpresso IDE (v11.6.1) but it does not compile. After fixing some easy header omissions it stalls on CMSIS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

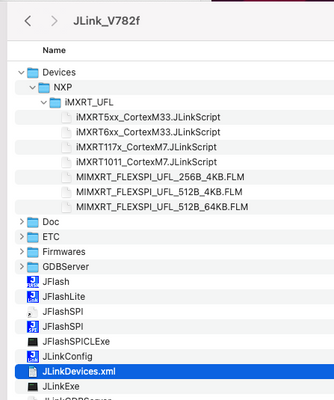

Hi @mrecoskie ,

Just download the package and copy Device folder and JLINKDevices.xml to JLink install folder. That's all. My jlink driver is v7.82c.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My jlink driver is v7.82f. I copied the ‘Devices’ folder and JLinkDevices.xml to the Jlink install folder except nothing unique comes up under 'Device' to select in the MCUXpresso Debug Configurations. What should I expect here?

Thanks,

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Type "MIMXRT1050_UFL_L0" here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks. This gets farther in the Debugger.

I see the flash written. I see the ResetISR symbol come up in the Debug window but then the program stalls with no symbols to show what is running.

I haven’t been able to find a way through the MCUXpresso IDE to debug this further. A breakpoint in the program does not seem to be executing. Running the program off the flash does not work.

How can I find where the processor is stuck?

In SystemInit the program runs until the ‘SystemInitHook()’ but gets no further.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content