- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: IMX8MM DDR Stress Tool test stuck

IMX8MM DDR Stress Tool test stuck

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IMX8MM DDR Stress Tool test stuck

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

I have a custom imx8mm board with a 512MB DDR4 (K4A4G165WE-BCTD).

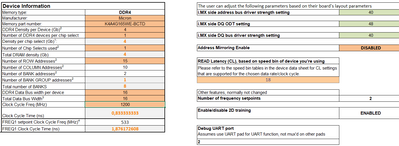

I want to do the DDR stress test (following the User guide). For that, I configured the DDR4 parameters in the MX8M_Mini_DDR4_RPA_v20.xls

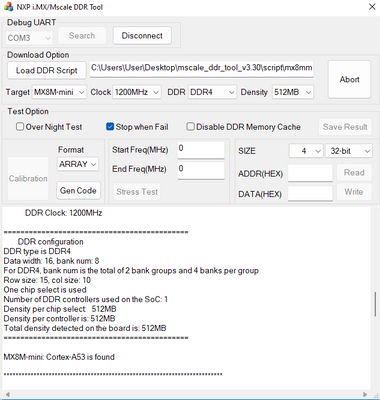

I did the calibration with these parameters in the Mscale DDR Tool:

But whhen I tried to do the Stress Test, it stuck's here:

Downloading file 'bin\ddr4_train1d_string_v201709.bin' ..Done

Downloading file 'bin\ddr4_train2d_string_v201709.bin' ..Done

Downloading file 'bin\ddr4_imem_1d_v201709.bin' ..Done

Downloading file 'bin\ddr4_dmem_1d_v201709.bin' ..Done

Downloading file 'bin\ddr4_imem_2d_v201709.bin' ..Done

Downloading file 'bin\ddr4_dmem_2d_v201709.bin' ..Done

Downloading IVT header...Done

Downloading file 'bin\m845s_ddr_stress_test.bin' ...Done

Download is complete

Waiting for the target board boot...

===================hardware_init=====================

hardware_init exit

*************************************************************************

*************************************************************************

*************************************************************************

MX8 DDR Stress Test V3.30

Built on Nov 24 2021 13:30:14

*************************************************************************

Waiting for board configuration from PC-end...

--Set up the MMU and enable I and D cache--

- This is the Cortex-A53 core

- Check if I cache is enabled

- Enabling I cache since it was disabled

- Push base address of TTB to TTBR0_EL3

- Config TCR_EL3

- Config MAIR_EL3

- Enable MMU

- Data Cache has been enabled

- Check system memory register, only for debug

- VMCR Check:

- ttbr0_el3: 0x93d000

- tcr_el3: 0x2051c

- mair_el3: 0x774400

- sctlr_el3: 0xc01815

- id_aa64mmfr0_el1: 0x1122

- MMU and cache setup complete

*************************************************************************

ARM clock(CA53) rate: 1200MHz

DDR Clock: 1200MHz

============================================

DDR configuration

DDR type is DDR4

Data width: 16, bank num: 8

For DDR4, bank num is the total of 2 bank groups and 4 banks per group

Row size: 15, col size: 10

One chip select is used

Number of DDR controllers used on the SoC: 1

Density per chip select: 512MB

Density per controller is: 512MB

Total density detected on the board is: 512MB

============================================

MX8M-mini: Cortex-A53 is found

*************************************************************************

============ Step 1: DDRPHY Training... ============

---DDR 1D-Training @1200Mhz...

[Process] End of initialization

[Process] End of read enable training

[Process] End of fine write leveling

[Process] End of read DQ deskew training

[Process] End of MPR read delay center optimization

[Process] End of Write Leveling coarse delay

[Process] End of write delay center optimization

[Process] End of read delay center optimization

[Process] End of max read latency training

[Result] PASS

---DDR 1D-Training @533Mhz...

[Process] End of initialization

[Process] End of read enable training

[Process] End of fine write leveling

[Process] End of MPR read delay center optimization

[Process] End of Write Leveling coarse delay

[Process] End of write delay center optimization

[Process] End of read delay center optimization

[Process] End of max read latency training

[Result] PASS

---DDR 2D-Training @1200Mhz...

[Process] End of initialization

[Process] End of 2D read delay/voltage center optimization

[Process] End of 2D write delay/voltage center optimization

[Result] PASS

============ Step 2: DDR memory accessing... ============

Verifying DDR frequency point0@1200MHz.......Pass

Verifying DDR frequency point1@533MHz.......Pass

[Result] OK

============ Step 3: DDR parameters processing... ============

[Result] Done

Success: DDR Calibration completed!!!

DDR Stress Test Iteration 1

--------------------------------

--Running DDR test on region 1--

--------------------------------

t0.1: data is addr test

Can you help me? What I'm doing wrong?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you share us the DDR datasheet to us?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Of course.

https://download.semiconductor.samsung.com/resources/data-sheet/DS_K4A4G165WE_BC_I_Rev1_4-1.pdf

All the documentation are is here:

https://semiconductor.samsung.com/us/dram/ddr/ddr4/k4a4g165we-bctd/

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your configuration is right, how about your status in your side?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I will help check.