- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- IMX6ULL EIM synchronous write Address

IMX6ULL EIM synchronous write Address

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everyone,

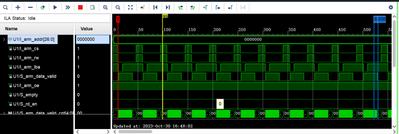

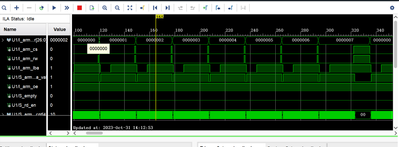

I am using the EIM interface of IMX6ULL and FPGA communication, using synchronous transmission (read write), 0x50000000 to 0x50000100 are the addresses corresponding to control commands, 0x50000200 to 0x50001000 are the addresses used for large amounts of data (DMA), the bus used is 16 bits (0-15), burst len=32.

1. In synchronous mode

At present, I have no problem writing control commands to 0x50000000, but when I write data to the address of 0x50000002, the FPGA still receives the address of 0x50000000.

But when I increase the address to 0x50000040 (32 * 2), I can write data again and the address is normal. Is this phenomenon related to burst len=32?

But I want to use the address 0x50000002, how can I solve this problem?

2 In asynchronous mode

I have no problem writing control commands to 0x50000000, and I can also write data to 0x50000002, but it will continue to be written to 0x50000004...... 0x5000000E, the written value is the same as 0x50000000, which affects the data in other addresses.

The following is in Chinese

大家好,

我使用的是IMX6ULL的EIM接口和FPGA通信,使用的是同步传输(读写).

0x50000000至0x50000100为控制命令对应的地址,0x50000200至0x50001000为大量数据(DMA)使用的地址,使用的总线为16位(0-15),burst len = 32.

1.在同步模式下

目前我往0x50000000写入控制命令没有问题,但是我往0x50000002的地址写入数据时,FPGA收到的地址仍然为0x50000000。

但是我将地址增在到0x50000040时(32*2),又可以写入数据了,地址也正常了。这个现象和burst len = 32有关系吗?

但是我想使用0x50000002这个地址,该如何解决这个问题?

2在异步模式下

我往0x50000000写入控制命令没有问题,也可以往0x50000002写入数据,但是会连续写入到0x50000004。。。。。。0x5000000E,写入的值和0x50000000一样,这样影响到其他的地址内的数据。

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

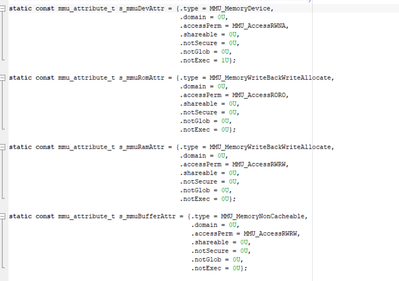

As with the previous question, the memory type setting is incorrect and should be set to

s_mmuDevAttr。

As shown in the following figure

还是内存初始化时的内存类型设置的不对,应该设置为

s_mmuDevAttr.

for (i = 0; i < 32; i++)

{

MMU_ConfigSection(MMU_L1Table, (const void *)(0x0C000000U + (i << 20)), (0x0C000000U + (i << 20)),

&s_mmuDevAttr); /* QSPI Rx Buf */

}

for (i = 0; i < 256; i++)

{

MMU_ConfigSection(MMU_L1Table, (const void *)(0x50000000U + (i << 20)), (0x50000000U + (i << 20)),

&s_mmuDevAttr); /* EIM */

}

for (i = 0; i < 256; i++)

{

MMU_ConfigSection(MMU_L1Table, (const void *)(0x60000000U + (i << 20)), (0x60000000U + (i << 20)),

&s_mmuRomAttr); /* QSPI */

}

for (i = 0; i < 2048; i++)

{

MMU_ConfigSection(MMU_L1Table, (const void *)(0x80000000U + (i << 20)), (0x80000000U + (i << 20)),

&s_mmuRamAttr); /* DDR */

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As with the previous question, the memory type setting is incorrect and should be set to

s_mmuDevAttr。

As shown in the following figure

还是内存初始化时的内存类型设置的不对,应该设置为

s_mmuDevAttr.

for (i = 0; i < 32; i++)

{

MMU_ConfigSection(MMU_L1Table, (const void *)(0x0C000000U + (i << 20)), (0x0C000000U + (i << 20)),

&s_mmuDevAttr); /* QSPI Rx Buf */

}

for (i = 0; i < 256; i++)

{

MMU_ConfigSection(MMU_L1Table, (const void *)(0x50000000U + (i << 20)), (0x50000000U + (i << 20)),

&s_mmuDevAttr); /* EIM */

}

for (i = 0; i < 256; i++)

{

MMU_ConfigSection(MMU_L1Table, (const void *)(0x60000000U + (i << 20)), (0x60000000U + (i << 20)),

&s_mmuRomAttr); /* QSPI */

}

for (i = 0; i < 2048; i++)

{

MMU_ConfigSection(MMU_L1Table, (const void *)(0x80000000U + (i << 20)), (0x80000000U + (i << 20)),

&s_mmuRamAttr); /* DDR */

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Levear,

- ARM (LDM / STM)

- ARM (VLDM / VSTM)

- i.MX SDMA.

Sanket Parekh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Levear,

I hope you are doing well.

If there are no further queries from your side, Can I mark this case as closed?

Thanks & Regards,

Sanket Parekh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content