- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

How to swap UART5 TX/RX in imx6

I use CSI0_DAT14 and CSI0_DAT15 for UART5 , on default , CSI0_DAT14 = UART5_RX and CSI0_DAT15 = UART5_TX, But I want to swap them, so in my dts file i change as following:

pinctrl_uart5_1: uart5grp-1 {

fsl,pins = <

MX6QDL_PAD_CSI0_DAT14__UART5_TX_DATA 0x1b0b1

MX6QDL_PAD_CSI0_DAT15__UART5_RX_DATA 0x1b0b1

>;

};

But it doesn't work. Can you give a hint for the solution.

Thanks

hey,

i enabled the uart5 in imx6 reference board but read write operations is not happening, is there any process to test the enabled uart5 port is working properly?

Hello,

When configuring GPIO, Pin tools may be useful; it also contains DTS for init.

Summary page :

Pins Tool for i.MX Application Processors|NXP

In particular for Your case :

- pin_list:

- {pin_num: M4, peripheral: UART5, signal: txd_mux, pin_signal: CSI0_DAT14}

- {pin_num: M5, peripheral: UART5, signal: rxd_mux, pin_signal: CSI0_DAT15}

* BE CAREFUL MODIFYING THIS COMMENT - IT IS YAML SETTINGS FOR TOOLS ***********

*/

fsl,pins = <

MX6QDL_PAD_CSI0_DAT14__UART5_TX_DATA 0x0001B0B0

MX6QDL_PAD_CSI0_DAT15__UART5_RX_DATA 0x0001B0B0

>;

Note, according to Pad Mux Register IOMUXC_SW_MUX_CTL_PAD_CSI0_DATA15 description,

in order to select signal UART5_RX_DATA (in ALT3 mode) it is necessary configure register IOMUXC_UART5_UART_RX_DATA_SELECT_INPUT for mode ALT3.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hello,

You can use definitions in Your pinfunc.h file ( say, located in /arch/arm/boot/dts/imx6dl-pinfunc.h)

As an example :

linux/arch/arm/boot/dts/imx6dl-pinfunc.h - Elixir - Free Electrons

There two definitions for CSI0_DAT14 pin may be found :

MX6QDL_PAD_CSI0_DAT14__UART5_TX_DATA

and

MX6QDL_PAD_CSI0_DAT14__UART5_RX_DATA

Actual IOMUXC register settings are provided in the definition lines,

assuming the following structure <mux_reg conf_reg input_reg mux_mode input_val>,

providing offsets for IOMUXC base address. Please check if input reg and corresponding

input_val fields are correct for Your case : input_reg = 0x91C , input_val = 01.

For more details refer to IOMUXC chapter of the RM. It may be needed to modify

the pinfunc file and rebuild kernel. The needed definition of (UART) pin may be

applied if the DTS file, for example as following :

linux-2.6-imx.git - Freescale i.MX Linux Tree

Regards,

Yuri.

Hi Yuri,

Thank you for your reply. But it does not work so far. I tested with both cases , but the result is the same,

case 1: I set dts as

pinctrl_uart5_1: uart5grp-1 {

fsl,pins = <

MX6QDL_PAD_CSI0_DAT14__UART5_TX_DATA 0x1b0b1

MX6QDL_PAD_CSI0_DAT15__UART5_RX_DATA 0x1b0b1

>;

};

after linux boot, I check the value of IOMUXC_UART5_UART_RX_DATA_SELECT_INPUT, it is 3 ,

and M4 is TX , i can see the data on M4 (no signal on M5) when sending.

case 2: I set dts as

pinctrl_uart5_1: uart5grp-1 {

fsl,pins = <

MX6QDL_PAD_CSI0_DAT14__UART5_RX_DATA 0x1b0b1

MX6QDL_PAD_CSI0_DAT15__UART5_TX_DATA 0x1b0b1

>;

};

after linux boot, I check the value of IOMUXC_UART5_UART_RX_DATA_SELECT_INPUT, it is 2 ,

but M4 is still TX , i still can see the data on M4(no signal on M5) when sending.

So i doubt wether it is the bug of the CPU . Is there any one who used M5 as TX successfully.

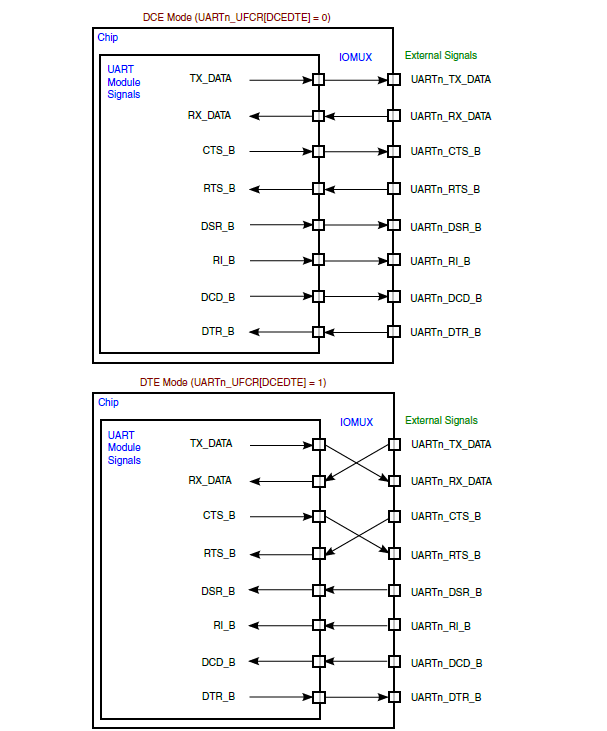

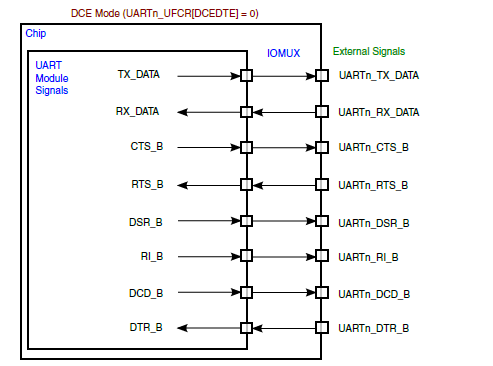

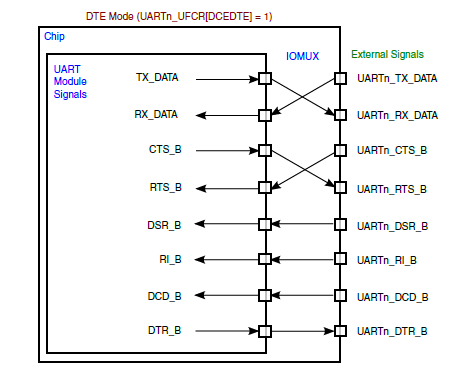

Please refer to imx6ull-14x14-evk.dts

all the i.MX6 family use the same mechanism.

1. configure the IOMUX to swap the pin.

2. tell uart module DTE or DCE mode.

please check the reference manual

690 &uart2 {

691 pinctrl-names = "default";

692 pinctrl-0 = <&pinctrl_uart2>;

693 fsl,uart-has-rtscts;

694 /* for DTE mode, add below change */

695 /* fsl,dte-mode; */

696 /* pinctrl-0 = <&pinctrl_uart2dte>; */

697 status = "okay";

698 };

hi,

UART5:

In dtsi file: Changes Done

pinctrl_uart5: uart5grp {

fsl,pins = <

MX6QDL_PAD_CSI0_DAT14__UART5_TX_DATA 0X13059

MX6QDL_PAD_CSI0_DAT15__UART5_RX_DATA 0X13059

>;

};

&uart5 {

pinctrl-names = "default";

pinctrl-0=<&pinctrl_uart5>;

compatible = "fsl,imx21-uart";

status = "okay";

};

Test Cases:

root@bhaggu:~# cat /proc/tty/driver/IMX-uart

serinfo:1.0 driver revision:

0: uart:IMX mmio:0x02020000 irq:58 tx:1219 rx:27 RTS|DTR|DSR|CD

4: uart:IMX mmio:0x021F4000 irq:62 tx:0 rx:0 DSR|CD

After Connecting Loopback(tx->rx) the results are as follows,

root@bhagguu:~# echo "bhagavan" > /dev/ttymxc4

root@bhagguu:~# echo "bhagavan" > /dev/ttymxc4

root@bhaggu:~# cat /proc/tty/driver/IMX-uart

serinfo:1.0 driver revision:

0: uart:IMX mmio:0x02020000 irq:58 tx:1757 rx:121 RTS|DTR|DSR|CD

4: uart:IMX mmio:0x021F4000 irq:62 tx:20 rx:20 DSR|CD

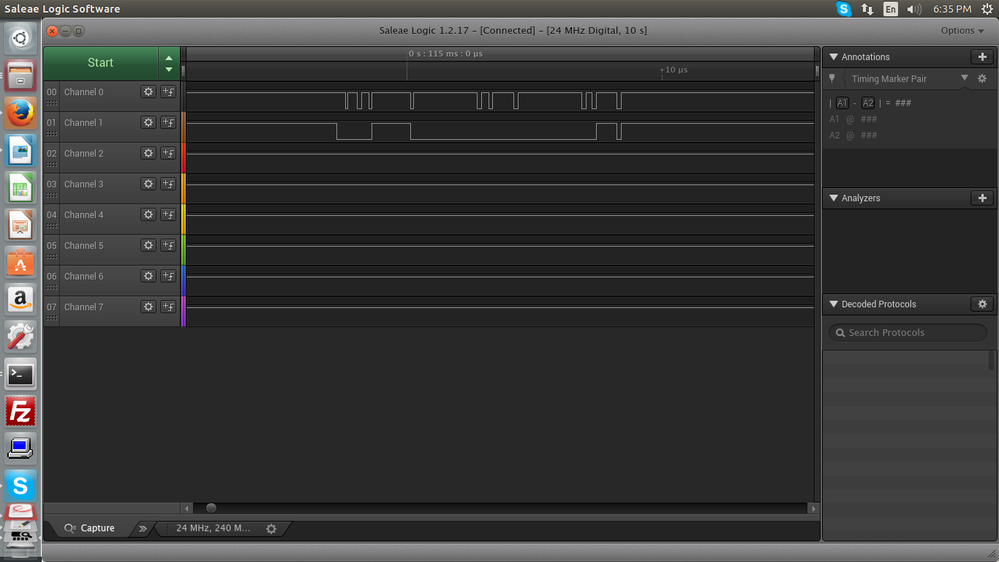

logic analyzer o/p: when sending data # echo "bhagavan" > /dev/ttymxc4

The above response is what i am getting, but how can i justify that the UART is working properly or not?

is there any test cases to run in the target board to ensure UART is working properly?

is there any loopback test to perform so that i could see the data what i transmitted?

Thanks&Regards,

bhagavan.

I did not see your dts tell i.MX6 it is DTE by the keyword fsl,dte-mode; which is in the binding guide.

It is very easy, just swap pin, tell the i.MX6 DCE or DTE mode as previous reply.

In you case,

DCE

pinctrl_uart5: uart5grp {

fsl,pins = <

MX6QDL_PAD_CSI0_DAT14__UART5_TX_DATA 0X13059

MX6QDL_PAD_CSI0_DAT15__UART5_RX_DATA 0X13059

>;

};

690 &uart5 {

691 pinctrl-names = "default";

692 pinctrl-0 = <&pinctrl_uart5>;

693 fsl,uart-has-rtscts;

697 status = "okay";

698 };

DTE:

pinctrl_uart5dte: uart5dtegrp {

fsl,pins = <

MX6QDL_PAD_CSI0_DAT14__UART5_RX_DATA 0X13059

MX6QDL_PAD_CSI0_DAT15__UART5_TX_DATA 0X13059

>;

};

&uart5 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart5dte>;

fsl,uart-has-rtscts;

fsl,dte-mode;

status = "okay";

};

example in 6ul:

DCE:

690 &uart2 {

691 pinctrl-names = "default";

692 pinctrl-0 = <&pinctrl_uart2>;

693 fsl,uart-has-rtscts;

694 /* for DTE mode, add below change */

695 /* fsl,dte-mode; */

696 /* pinctrl-0 = <&pinctrl_uart2dte>; */

697 status = "okay";

698 };

446 pinctrl_uart2: uart2grp {

447 fsl,pins = <

448 MX6UL_PAD_UART2_TX_DATA__UART2_DCE_TX 0x1b0b1

449 MX6UL_PAD_UART2_RX_DATA__UART2_DCE_RX 0x1b0b1

450 MX6UL_PAD_UART3_RX_DATA__UART2_DCE_RTS 0x1b0b1

451 MX6UL_PAD_UART3_TX_DATA__UART2_DCE_CTS 0x1b0b1

452 >;

-----------------------------------------------------

DTE:

690 &uart2 {

691 pinctrl-names = "default";

692 /* pinctrl-0 = <&pinctrl_uart2>; */

693 fsl,uart-has-rtscts;

694 /* for DTE mode, add below change */

695 fsl,dte-mode;

696 pinctrl-0 = <&pinctrl_uart2dte>;

697 status = "okay";

698 };

455 pinctrl_uart2dte: uart2dtegrp {

456 fsl,pins = <

457 MX6UL_PAD_UART2_TX_DATA__UART2_DTE_RX 0x1b0b1

458 MX6UL_PAD_UART2_RX_DATA__UART2_DTE_TX 0x1b0b1

459 MX6UL_PAD_UART3_RX_DATA__UART2_DTE_CTS 0x1b0b1

460 MX6UL_PAD_UART3_TX_DATA__UART2_DTE_RTS 0x1b0b1

461 >;

462 };

This is an old thread and helped a lot to finally clarify things.

Only one note. Picture with straight connections should be named DTE. Becouse internally cross-wired TX - > RX is tipical of a DCE device (modem) that received signals on TX. Please correct me if i am wrong, it's just to clarify.

understand your point. But it is i.MX6 special pin name and requirement. we ask designer follow the i.MX6 pin name. The same is for the ethernet connections. i.MX6 asks TX connect to TX phy side. For the uart case, TX to TX the fifo inside the chip, which is not shown here in the diagram, is RX to TX. For swap, the IOMUX does the first swap for TX/RX, which need daisy iomux help and the "fsl,dte" is the second swap by the internal fifo. I totally agree with you in the protocol layer. TX to RX is DCE. TX to TX is DTE. But we need to follow the chip design and the BSP, right?

Hi Biyong,

thanks for pointing out the reasons. This thread is really good, pictures here above clear any doubt and helps a lot.

So, if i understand properly, you have finally a dual swap. So if so, all is clear now.

Old guys knows that DTE to DTE requires a null-modem (swapped) cable, and DTE to DCE a straight one.

But for the current case, DTE and DCE are just names, and at the end is not even importand who is who. It's likely more important proper connection.

Thanks,

angelo

hi jerry Yan,

have you already solved this issue? i meet same situation.

it sames that this issue have not been solved. i modify the dts file, found that daisy register would be configured according to dts macro value.