- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: How to program hyperflash S26HL512T on RT1176 with JLink/MCUXpresso?

How to program hyperflash S26HL512T on RT1176 with JLink/MCUXpresso?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have a custom board with RT1176 mcu and S26HL512T Infineon hyperflash ( it is basically the newer version of the previous one - Migrating from S26KL-S/S26KS-S HYPERFLASH™ to S26HL-T/S26HS-T SEMPER™ flash with HYPERBUS™ (infineon... ) on the PCB. I wrote a driver for it and it works correctly when code is linked to RAM and executed from there.

However, It was high time I used JLink/MCUXpresso to do the flashing because I wanted to run the code in XIP mode. The steps I followed are listed below.

1.) I became aware that I needed a proper flashdriver for my code to be programmed into hyperflash via Jlink/MCUXpresso, so I decided to modify some existing hyperflash driver for some other mcu (1052 it was I think), compiled LPCXFlashDriverLib as release and my modified hyperflash driver and it generated MIMXRT1050-EVK_S26KS512S.cfx( the old name was left, but the image build was a new one because I checked the date of modification. I will need to change that name some time later).

2.) I also noticed that I needed some "special" device .xml description file for my case (I followed this thread: https://www.cnblogs.com/henjay724/p/14942574.html). I copied the necessary files so that my device was visible from the JFLASH tool. I was able to choose a device from the list afterwards. I also made sure to set proper WorkRAMAddr(0x20240000/many different ones were tried too :D) and Flash BaseAddrstart (0x30000000 for FLEXSPI1).

Unfortunately I was not able to get it to work (neither of MIMXRT1170_UFL_L0/L1/L2 would work for my case), because programming would fail upon executing RAM coded functions (from that I thought it was problem on the JLink side but I'm not 100% sure).

3.) I started to go through the ufl source code and noticed that it may not work out of the box for my case, because there are subtle differences between the hyperflash that was tested for the current UFL 1.0 release and the newer ones that are available.

So it seems like CFI is no longer there and the coded procedure will not work properly for that chip.

However, I can also modify the code "hard code" the proper values that are required here and there.

Additionally, default page size is not 512B but 256B, which can also be easily changed in the code to correspond with the proper setting of hyperflash memory. That part I need to test out tomorrow, because I do not have access to the hardware right now.

I suspect that there are couple of reasons why programming code into hyperflash does not work for me:

- https://community.nxp.com/t5/i-MX-RT/Cannot-flash-RT1170-EVK-with-OctalSPI-Flash-enabled/m-p/1289520... -> NXP supp basically says that for rt1170, special .dll is required for JLink), maybe I'm missing something?

- Minor differences with the ufl generated image using no longer valid parameters (512B page size instead of 256B) and registers(No more CFI register).

I'm still trying to wrap this whole process around my head to better understand how it works and what is the relation with JLink, Jlinkscript, flash driver and so on.

Sorry for the long post, I hope someone will be able to help. Please let me know what details you need to get better understanding of the situation.

Thanks,

Michael

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm coming back with a solution to my problem.

The culprit was the whole time (or so I choose to believe) in the debug session configuration itself!!

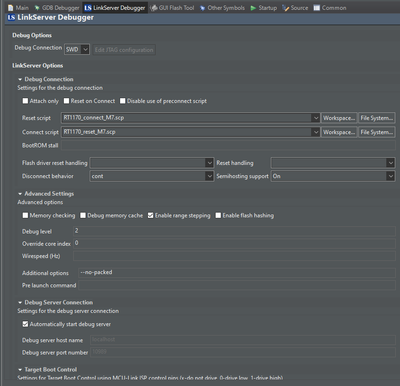

Take a look at the image below.

Do note that upon creation of a new debug configuration instance for Link Server, the RESET HANDLING method is not set to anything, it is just a blank field. One must explicitly choose one of the available methods from the drop down window.

I do not know whether it was intentional in order for some compliancy matters or some sort of safety precaution, but for me it seems like something not obvious at first. Why it could not be set to default value as in the previous image?

Anyway, I'm glad to have that thing sorted, now is time to take on next problems and challenges

Thanks,

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm coming back with a solution to my problem.

The culprit was the whole time (or so I choose to believe) in the debug session configuration itself!!

Take a look at the image below.

Do note that upon creation of a new debug configuration instance for Link Server, the RESET HANDLING method is not set to anything, it is just a blank field. One must explicitly choose one of the available methods from the drop down window.

I do not know whether it was intentional in order for some compliancy matters or some sort of safety precaution, but for me it seems like something not obvious at first. Why it could not be set to default value as in the previous image?

Anyway, I'm glad to have that thing sorted, now is time to take on next problems and challenges

Thanks,

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @mimlo,

First of all, we apologize for the delay to answer you.

To start, could you please take a look to the following information?

- Tutorial: MCUXpresso SDK with Linux, Part 3: RAM and XiP Code on i.MX RT1064 | MCU on Eclipse

- Using SEGGER J-Link with QSPI FLASH on NXP i.MX Boards | MCU on Eclipse

- Solved: How to program hyperflash S26KS512 on rt1170 with ... - NXP Community

- Working RT1062xxxxB HyperFLASH device in JLINKDevi... - NXP Community

They could be useful.

Best regards, Raul.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raul,

Unfortunately neither of the links you provided were helpful as I was already familiar with them at the time of writing my post.

In my opinion, currently used version of ROM API is not compatible with the hyperflash I'm using, because every configuration I tried to use reports error saying that flash device is not recognized.

Recently decided to abandon the jlink approach and use MIMXRT1170 EVB and its CMSIS-DAP programmer (I had to disconnect some of the jumpers to achieve that).

Now I'm feeling like the process of flashing the firmware is going much further that it did with jlink approach. However, I still have issues.

I get the following error:

ChecksumSectors (0x30000000, 0x2000F668, 0x1) status 0x3 - driver reported driver error - EXTSPIJ driver

No matter which FlashDeviceV_t device type I use (EXTSPI, EXTSPIJ, UNKNOWN) I get the same result.

It is worth to note that after that error, writing firmware bytes is processing until the end, after being complete, mem fault happen and the code wild (probably because of the incorrect SP value).

Do you have any idea on what could be done here? What more information do you need to be able to point me in the correct direction?

PS. Tomorrow I will post some screenshots of the console messages and errors.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Since I decided to try out the MCU-Link debug probe using CMSIS-DAP debug interface, it seems like the process of programming the board is going much better, however issues still persist and I'm still unable to program the board and run code correctly.

Note: I'm using NXP MCU-LINK programmer with MCUXPRESSO IDE 11.7.1.

In order to prepare the flash driver for my S26HL512T hyperflash, I copied an example of flash driver for a different MCU and hyperflash version. I ported my solution to the existing one and tested it with a proper linker file dedicated for flash driver tests. Then I run the test from main and got a success, meaning that driver worked correctly.

Basically I followed this guide from the knowledge base section from NXP:

How to create a new Flash driver of the MCUXPresso... - NXP Community

Then I built the flash driver with some needed modification to the following files:

1.) FlashDev.c

2.) FlashPrg.c

1.) My FlashDeviceV_t FlashDevice structure looks like this:

FlashDeviceV_t FlashDevice = {

FLASH_DRV_VERS, // Driver Version, do not modify!

"HyperFlash_GEORGE"__DATE__" "__TIME__,

EXTSPIJ, // Device Type

FlexSPI1_AMBA_BASE, // Device Start Address: (0x30000000U)

FLASH_SIZE_Bytes, // Device Size: (0x4000000)

FLASH_PAGE_SIZE_Bytes, // Programming Page Size: 256U

0, // Reserved, must be 0

0xFF, // Initial Content of Erased Memory

3000, // Program Page Timeout

6000, // Erase Sector Timeout

// Specify Size and Address of Sectors

{{FLASH_SECTOR_SIZE_Bytes, 0}, // Sector sizes: (0x40000)

{SECTOR_END}}

};

The defines used in the struct have their values defined in the code comments to the right.

2.) In this source file I just updated functions such as ProgramPage, EraseSectors and EraseChip to use my hyperflash low level driver (which I wrote some time ago and confirmed that it works).

Once I build LPCXFlashDriverLib without sector hashing and then compiled the newly created flash driver I created the LinkServer debug configuration which looks like on the images below:

I had to turn of "enable flash hashing" option because I build the LPCXFlashDriverLib without flash hashing enabled.

I also decided to use GUI Flash Tool to see the results of erasing, checking blanks and programming the image to the memory

(as recommended here: User loadable flash drivers - NXP Community).

After executing the tool I confirmed that erasing and checking for blanks via the GUI Flash Tool results in a success. I also run the code as "linked to ram" and then while being stopped on the breakpoint I checked the memory view tab in order to see the contents of the flash starting from address 0x30000000 which is the base of flash. I did that after erasing to confirm that the sectors contain only 0xFF values, as well as after writing the code via the tool, in order to see any change in flash memory. The change was visible and code was written to the memory.

Proof of the GUI Flash Tool operation is on the console log below:

xecuting flash operation 'Erase' (Erase flash) - Wed Sep 27 11:16:14 CEST 2023

Checking MCU info...

Scanning for targets...

Executing flash action...

MCUXpresso IDE RedlinkMulti Driver v11.7 (Mar 22 2023 09:52:55 - crt_emu_cm_redlink.exe build 13)

( 0) Reading remote configuration

Wc(03). No cache support.

Found chip XML file in C:/NXP_MCU/Tools/test_application_IMXRT1170/test_application_rt1170/Debug\MIMXRT1176xxxxx.xml

( 5) Remote configuration complete

Reconnected to existing LinkServer process.

============= SCRIPT: RT1170_connect_M7.scp =============

RT1170 Connect M7 Script

DpID = 6BA02477

APID = 0x84770001

View cores on the DAP AP

TAP 0: 6BA02477 Core 0: M7 APID: 84770001 ROM Table: E00FD003*

============= END SCRIPT ================================

Probe Firmware: MCU-LINK (r0FF) CMSIS-DAP V3.108 (NXP Semiconductors)

Serial Number: ZJCMPCKNXCEPV

VID:PID: 1FC9:0143

USB Path: 0002:0005:00

Using memory from core 0 after searching for a good core

( 30) Emulator Connected

( 40) Debug Halt

( 50) CPU ID

debug interface type = CoreSight DP (DAP DP ID 6BA02477) over SWD TAP 0

processor type = Cortex-M7 (CPU ID 00000C27) on DAP AP 0

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 6BA02477. CpuID: 00000C27. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FD000: CID B105100D PID 000008E88C ROM (type 0x1)

ROM 1 E00FE000: CID B105100D PID 04000BB4C8 ROM (type 0x1)

ROM 2 E00FF000: CID B105100D PID 04000BB4C7 ROM (type 0x1)

ROM 3 E000E000: CID B105E00D PID 04000BB00C Gen SCS (type 0x0)

ROM 3 E0001000: CID B105E00D PID 04000BB002 Gen DWT (type 0x0)

ROM 3 E0002000: CID B105E00D PID 04000BB00E Gen (type 0x0)

ROM 3 E0000000: CID B105E00D PID 04000BB001 Gen ITM (type 0x0)

ROM 2 E0041000: CID B105900D PID 04001BB975 CSt ARM ETMv4.0 type 0x13 Trace Source - Core

ROM 2 E0042000: CID B105900D PID 04004BB906 CSt type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0043000: CID B105900D PID 04001BB908 CSt CSTF type 0x12 Trace Link - Trace funnel/router

NXP: MIMXRT1176xxxxx

DAP stride is 1024 bytes (256 words)

Inspected v.2 External Flash Device on SPI using SFDP JEDEC ID MIMXRT1176-imxrt1176MCU_S26HL512T.cfx

Image 'HyperFlash_imxrt1176MCUSep 22 2023 15:47:18'

( 65) Chip Setup Complete

Connected: was_reset=true. was_stopped=false

( 70) License Check Complete

Opening flash driver MIMXRT1176-imxrt1176MCU_S26HL512T.cfx

Sending VECTRESET to run flash driver

Flash device supported (64MB = 256*256K at 0x30000000)

Mass Erase flash at 0x30000000

Closing flash driver MIMXRT1176-imxrt1176MCU_S26HL512T.cfx

MassErase completed (in 228256ms)

Hhaving confirmed that the GUI Flash Tool seems to work fine and no error are reported back from the tool, I tried to program the code using MCUXpresso Debug session.

Unfortunately it resulted in a failure and the debug log is pasted below:

MCUXpresso IDE RedlinkMulti Driver v11.7 (Mar 22 2023 09:52:55 - crt_emu_cm_redlink build 13)

Found chip XML file in C:/NXP_MCU/Tools/test_application_IMXRT1170/test_application_rt1170/Debug\MIMXRT1176xxxxx.xml

( 5) Remote configuration complete

Reconnected to existing LinkServer process.

============= SCRIPT: RT1170_reset_M7.scp =============

SOFT Reset (RAM)

Vector table SP/PC is the reset context.

PC = 0x6C47CE1B

SP = 0xBC425F8D

XPSR = 0x01000000

VTOR = 0x00000000

Set DEMCR = 0x010007F1

============= END SCRIPT ==============================

Probe Firmware: MCU-LINK (r0FF) CMSIS-DAP V3.108 (NXP Semiconductors)

Serial Number: ZJCMPCKNXCEPV

VID:PID: 1FC9:0143

USB Path: 0002:0005:00

Using memory from core 0 after searching for a good core

( 30) Emulator Connected

debug interface type = CoreSight DP (DAP DP ID 6BA02477) over SWD TAP 0

processor type = Cortex-M7 (CPU ID 00000C27) on DAP AP 0

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 6BA02477. CpuID: 00000C27. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FD000: CID B105100D PID 000008E88C ROM (type 0x1)

ROM 1 E00FE000: CID B105100D PID 04000BB4C8 ROM (type 0x1)

ROM 2 E00FF000: CID B105100D PID 04000BB4C7 ROM (type 0x1)

ROM 3 E000E000: CID B105E00D PID 04000BB00C Gen SCS (type 0x0)

ROM 3 E0001000: CID B105E00D PID 04000BB002 Gen DWT (type 0x0)

ROM 3 E0002000: CID B105E00D PID 04000BB00E Gen (type 0x0)

ROM 3 E0000000: CID B105E00D PID 04000BB001 Gen ITM (type 0x0)

ROM 2 E0041000: CID B105900D PID 04001BB975 CSt ARM ETMv4.0 type 0x13 Trace Source - Core

ROM 2 E0042000: CID B105900D PID 04004BB906 CSt type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0043000: CID B105900D PID 04001BB908 CSt CSTF type 0x12 Trace Link - Trace funnel/router

NXP: MIMXRT1176xxxxx

DAP stride is 1024 bytes (256 words)

Inspected v.2 External Flash Device on SPI using SFDP JEDEC ID MIMXRT1176-imxrt1176MCU_S26HL512T.cfx

Image 'HyperFlash_imxrt1176MCUSep 22 2023 15:47:18'

( 65) Chip Setup Complete

Connected: was_reset=true. was_stopped=false

Awaiting telnet connection to port 3330 ...

GDB nonstop mode enabled

Opening flash driver MIMXRT1176-imxrt1176MCU_S26HL512T.cfx

Sending VECTRESET to run flash driver

Flash device supported (64MB = 256*256K at 0x30000000)

Writing 37244 bytes to address 0x30000000 in Flash

30000300 done 2% (768 out of 37244)

( 2) at 30000300: 256 bytes - 1024/37244

30000600 done 4% (1536 out of 37244)

30000900 done 6% (2304 out of 37244)

30000C00 done 8% (3072 out of 37244)

30000F00 done 10% (3840 out of 37244)

30001200 done 12% (4608 out of 37244)

30001500 done 14% (5376 out of 37244)

30001800 done 16% (6144 out of 37244)

30001B00 done 18% (6912 out of 37244)

30001E00 done 20% (7680 out of 37244)

30002100 done 22% (8448 out of 37244)

30002400 done 24% (9216 out of 37244)

30002700 done 26% (9984 out of 37244)

30002A00 done 28% (10752 out of 37244)

30002D00 done 30% (11520 out of 37244)

30003000 done 32% (12288 out of 37244)

30003300 done 35% (13056 out of 37244)

30003600 done 37% (13824 out of 37244)

30003900 done 39% (14592 out of 37244)

30003C00 done 41% (15360 out of 37244)

30003F00 done 43% (16128 out of 37244)

30004200 done 45% (16896 out of 37244)

30004500 done 47% (17664 out of 37244)

30004800 done 49% (18432 out of 37244)

30004B00 done 51% (19200 out of 37244)

30004E00 done 53% (19968 out of 37244)

30005100 done 55% (20736 out of 37244)

30005400 done 57% (21504 out of 37244)

30005700 done 59% (22272 out of 37244)

30005A00 done 61% (23040 out of 37244)

30005D00 done 63% (23808 out of 37244)

30006000 done 65% (24576 out of 37244)

30006300 done 68% (25344 out of 37244)

30006600 done 70% (26112 out of 37244)

30006900 done 72% (26880 out of 37244)

30006C00 done 74% (27648 out of 37244)

30006F00 done 76% (28416 out of 37244)

30007200 done 78% (29184 out of 37244)

30007500 done 80% (29952 out of 37244)

30007800 done 82% (30720 out of 37244)

30007B00 done 84% (31488 out of 37244)

30007E00 done 86% (32256 out of 37244)

30008100 done 88% (33024 out of 37244)

30008400 done 90% (33792 out of 37244)

30008700 done 92% (34560 out of 37244)

30008A00 done 94% (35328 out of 37244)

30008D00 done 96% (36096 out of 37244)

30009000 done 98% (36864 out of 37244)

Erased/Wrote sector 0-0 with 37244 bytes in 3554msec

Closing flash driver MIMXRT1176-imxrt1176MCU_S26HL512T.cfx

Flash Write Done

Flash Program Summary: 37244 bytes in 3.55 seconds (10.23 KB/sec)

============= SCRIPT: RT1170_connect_M7.scp =============

RT1170 Connect M7 Script

DpID = 6BA02477

APID = 0x84770001

View cores on the DAP AP

TAP 0: 6BA02477 Core 0: M7 APID: 84770001 ROM Table: E00FD003*

============= END SCRIPT ================================

16: Target error from status-poll: Nn(05). Wire ACK Fault in DAP access

From the above I think that the process of writing the data completes without any issues, but the process of trying to start the code is where the process fails.

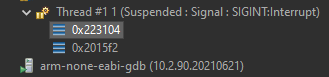

After the process fails I get the following:

or

I suspect that it's the issue of Program Counter (PC) being set to some garbage value but I'm no expert here.

PS:

Sorry for the long post but I tried to give as much info for the context as I could.

I'm working for a company which has been using NXP products for a while now, and probably we will need to sign the NDA regarding encryption topic on the MCU. I really hope someone will be able to help us here. We are basically stuck and can't move that particular topic forward.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @mimlo,

Just for double check, could you please take a look at the Hyper Flash specifications in the MIMXRT1170 EVK Board Hardware User’s Guide. Section 2.6 Hyper Flash? There it is mentioned a setting that must be followed to enable the OCT Flash. Also, could you please take a look to Section 2.2 Boot mode configurations?

Best regards, Raul.