- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: Custom IMX28 board, no boot

Custom IMX28 board, no boot

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I design my own board with an imx28 CPU. I configured the board (resistors on LCD_D0 to LCD_05) to boot on SSP0 (SD card).

When I try to boot without SD card connected, I have the 0x8020a014 error code on the debug console. So it seems it want to boot on Sd card. So it's good.

But when I connect the SD card, I have absolutely nothing on the debug console.

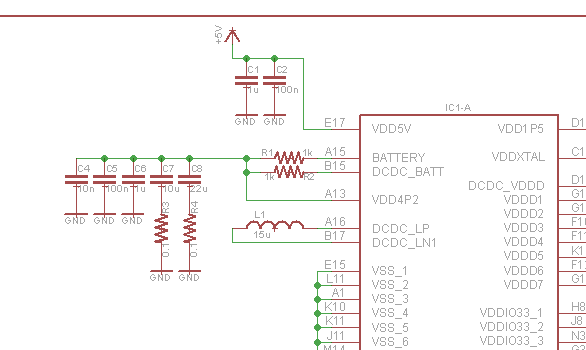

I measured voltage and everything is good except VDD4P2. It equal to 0.8V !!!!!

This is the schematic :

Can you help me ?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In order to close this topic, please find attached my patch for VDD5V Only and the patch for my DDR2 (Samsung K4T51163QQ-BCE7).

Finaly, these patchs are very simple.

To explain what my patches do :

In spl_power_init.c, I set DROPOUT_CTRL (in HW_POWER_DCDC4P2 register) to "DcDc Converter power source is DCDC_4P2 regardless of BATTERY voltage" instead of "DcDc converter selects either VDD4P2 or BATTERY, which ever is higher."

In spl_mem_init.c, I set CS_MAP (in HW_DRAM_CTL29 register) to 1 instead of 16 (?) and I set EIGHT_BANK_MODE (in HW_DRAM_CTL31 register) to "Memory devices have 4 banks" instead of "Memory devices have 8 banks".

In mx28evk.h, I set "define PHYS_SDRAM_1_SIZE" to 0x04000000 (64MB) instead of 0x40000000 (1GB).

Now, everything is fully stable. After 200 loops of 30MB test with memtester I have 0 error. All the supply from the IMX a solid and with a correct voltage.

Many thanks for all your help during these 3 months. This is the culmination :).

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In order to close this topic, please find attached my patch for VDD5V Only and the patch for my DDR2 (Samsung K4T51163QQ-BCE7).

Finaly, these patchs are very simple.

To explain what my patches do :

In spl_power_init.c, I set DROPOUT_CTRL (in HW_POWER_DCDC4P2 register) to "DcDc Converter power source is DCDC_4P2 regardless of BATTERY voltage" instead of "DcDc converter selects either VDD4P2 or BATTERY, which ever is higher."

In spl_mem_init.c, I set CS_MAP (in HW_DRAM_CTL29 register) to 1 instead of 16 (?) and I set EIGHT_BANK_MODE (in HW_DRAM_CTL31 register) to "Memory devices have 4 banks" instead of "Memory devices have 8 banks".

In mx28evk.h, I set "define PHYS_SDRAM_1_SIZE" to 0x04000000 (64MB) instead of 0x40000000 (1GB).

Now, everything is fully stable. After 200 loops of 30MB test with memtester I have 0 error. All the supply from the IMX a solid and with a correct voltage.

Many thanks for all your help during these 3 months. This is the culmination :).

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Damien,

I'm going to keep my U-Boot patch mostly as-is for a few reasons:

- The patch disables battery voltage measurement when there is no battery

- The patch disables all code paths relating to booting from battery

- The power block configuration is based primarily on the Fressscale bootlets which I think should be retained unless we can come up with some pretty clear and convincing arguments as to why an alternative approach is better

I think there is scope for some refactoring of the power block setup code in U-Boot, but for now I think it best to leave it as close to the bootlet code sequence as practical

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Change of plan...

I've confirmed Damien's patch works on the board I am developing for, so I will make the bare minimum of changes (i.e. Damien's patch). The rest can be worked on later

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Just would like to mention that Graeme/Damien's patch for 5V only operation has been applied:

Regards,

Fabio Estevam

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Damien,

That's great news :-) Glad to know your board is stable now.

Just to make sure I understood:

1. You only need to apply VDD5V_Only_Uboot.patch.zip in spl_power_init.c. The previous VDD5V_Only_Uboot_2014.patch.zip that you posted on January, 6th is no longer needed. Is that correct?

2. About the second patch: you could let DDR settings inside spl_mem_init.c untouched and then rewrite CTL29 and CTL31 using mxs_adjust_memory_params(). Please check board/bluegiga/apx4devkit/spl_boot.c as a reference.

Regards,

Fabio Estevam

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Fabio,

1 . About the patch posted on January, 6th, you can simply delete it, and empty your recycle bin :smileyhappy:. It generate DDR errors (I searched a long time in spl_mem_init to find why my DDR was not stable, but it was not a DDR configuration mistake, but a power mistake caused by my patch).

2. Perfect, many thanks for this advice.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I've finally managed to start U-Boot 2015.01-rc2 on my own board with VDD5V only.

I will now fix every little mistake then clean my code and post my patch.

But I still have two little problems.

1. U-Boot detects only 64Mib instead of 512Mib. This is my "include/configs/mx28_evk.h" file :

#define CONFIG_NR_DRAM_BANKS 4 /* 4 bank of DRAM */

#define PHYS_SDRAM_1 0x40000000 /* Base address */

#define PHYS_SDRAM_1_SIZE 0x20000000 /* 512 MB */

2. duart_tx don't work. When I have the message "Hit any key to stop autoboot:", I can press any key, U-boot launch autoboot.

I tried with a non-modified U-boot 2015.01-rc2 on mx28evk and the problem is also there. So I think is a problem on the U-boot code and not a problem due to my changes.

Was this problem already reported ?

Many thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Damien,

Good progress.

Let's try to fix the duart issue first: I have just tested top of tree U-boot on my mx28evk and duart works fine here (U-Boot 2015.01-rc3-00069-gfc9b0b8).

Make sure your terminal has flow control disabled.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for your answer.

It's a bug on the U-Boot 2015.01-rc2.

With U-Boot 2015.01-rc3 it works :smileyhappy: !

There were no modification on SPL_POWER_INIT.c and SPL_MEM_INIT.c between rc2 and rc3 so all my modifications are still good.

This I my debug output :

HTLLC

Configured for 5v only power source.

Valid 5V detected

sz =08000000

LLC

U-Boot 2015.01-rc3 (Dec 12 2014 - 15:26:45)

CPU: Freescale i.MX28 rev1.2 at 454 MHz

BOOT: SSP SD/MMC #0, 3V3

SPI: ready

DRAM: 128 MiB

NAND: 0 MiB

MMC: MXS MMC: 0

MMC0: Command 8 timeout (status 0xe0284020)

MMC0: Command 55 timeout (status 0xe0384020)

MMC0: Command 1 timeout (status 0xe02c4020)

Card did not respond to voltage select!

MMC init failed

Using default environment

Video: MXSFB: 'videomode' variable not set!

In: serial

Out: serial

Err: serial

Net: FEC0 [PRIME], FEC1

Warning: FEC1 using MAC address from net device

Hit any key to stop autoboot: 0

=>

Now, the boot fails during mxs_mem_get_size() function. Especially on this line : sz = get_ram_size((long *)PHYS_SDRAM_1, PHYS_SDRAM_1_SIZE);

If I force sz to be 512Mib (so replace the previous line by sz=0x20000000), U-boot stops here :

HTLLC

Configured for 5v only power source.

Valid 5V detected

sz = 20000000

LLC

U-Boot 2015.01-rc3 (Dec 12 2014 - 15:36:08)

CPU: Freescale i.MX28 rev1.2 at 454 MHz

BOOT: SSP SD/MMC #0, 3V3

SPI: ready

DRAM:

But if I force sz to be 128Mib (so sz=0x08000000), It works but with only 128Mib (see debug output above)

EDIT :

The following lines are normal because I launch U-boot with mxsldr, so I don't have any sd card on my board :

MMC0: Command 8 timeout (status 0xe0284020)

MMC0: Command 55 timeout (status 0xe0384020)

MMC0: Command 1 timeout (status 0xe02c4020)

Card did not respond to voltage select!

MMC init failed

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Damien,

The sz = get_ram_size((long *)PHYS_SDRAM_1, PHYS_SDRAM_1_SIZE); assumes that there is only one bank of RAM.

I suppose you use EMI_CE0 and EMI_CE1 for the DDR chip selects on your board, right? Then you should use CONFIG_NR_DRAM_BANKS 2.

You should also change the size calculation as follows:

sz1 = get_ram_size((long *)PHYS_SDRAM_1, PHYS_SDRAM_1_SIZE);

sz2 = get_ram_size((long *)PHYS_SDRAM_2, PHYS_SDRAM_2_SIZE);

sz = sz1 + sz2;

and then in your board config file you need to pass PHYS_SDRAM_2 and PHYS_SDRAM_2_SIZE definitions.

Also, you would need to adjust CS_MAP field to 3 in the HW_DRAM_CTL29 register to make use of the 2 Chip Selects.

In board/freescale/mx28evk/iomux.c we have:

#define CS_MAP 0xf as we use a single chip select.

you should change it to 3 for your board.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Damien,

Maybe the two changes below should be enough:

1. Change CS_MAP to 3

2. In the board config file use:

/* Memory configuration */

#define CONFIG_NR_DRAM_BANKS 1 /* 1 bank of DRAM */

#define PHYS_SDRAM_1 0x40000000 /* Base address */

#define PHYS_SDRAM_1_SIZE 0x40000000 /* Max 1 GB RAM */

#define CONFIG_SYS_SDRAM_BASE PHYS_SDRAM_1

I think this would allow U-boot to detect the correct memory size.

If that does not work, then we should consider changing sz calculation as mentioned in my previous post.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for your help.

I use a Samsung K4T51163QQ-BCE7.

This is the addressing configuration :

Configuration : 32Mb x16

# of Bank : 4

Bank Address : BA0,BA1

Auto precharge : A10/AP

Row Address : A0 ~ A12

Column Address : A0 ~ A9

I only use 1 chip select, EMI_CE0 (my DDR has only one pin CS). But the Bank is selected with EMI_BA0 and EMI_BA1.

So, I suppose I don't need to change anything to CS_MAP, isn't it ?

Many thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Damien,

The DDR you use is 512Mbits, which correspond to 64MBytes and you should use

| CONFIG_NR_DRAM_BANKS | 1 |

as only one chip select is used.

Yes, you don't need to change CS_MAP.

Regards,

Fabio Estevam

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Is the problem can only come from the DDR initialisation in the spl_mem_init ?

Because I retry a lot of time, I followed the excel tools scrupulously to set all the HW_DRAM_CTL register but I still have this error.

Many thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Are you able to boot the kernel on your board if you use bootlets instead? Does it boot without issues in this case?

I am not sure if the problem is bad DDR init or U-boot porting? Are the power supplies stable?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Maybe I found something.

The DDR2 our supplier provided us were not the DDR2-800 but DDR2-667 version ! So this DDR can not run at 200MHz. Do you know how to speed down the DDR clock to 166 MHz ?

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

If I recall correctly there is an entry in the Excel datasheet for the DDR frequency, so you should adjust it there.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Ok, I have set 166 MHz in the excel tool and in spl_mem_init i set divider (for HW_CLKCTRL_FRA0_EMI) to 26 (for 166 MHz).

But it still don't work.

I look at the scoope and the power supply is really solid. 1V8 is 1.81V and 4V2 is 4.24V.

On the imx28evk, everything works fine

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Damien,

I made some changes to the patches you made for the memory and now I'm able to start Linux on your custom board :-)

Image is build using Yocto Dizzy. Only quick test I did now are a couple of reboots to check if the board starts up into Linux.

I will included a memory tester program in the image so we are able to do a complete test of the memory range and test stability of this memory configuration.

I will mail you the different patches and memory configurator file.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mario,

This is great news! By "I will included a memory tester program in the image" do you mean to use the memtester program?

Regards,

Fabio Estevam